Timer/PWM Module (S08TPMV3)

MCF51QE128 MCU Series Reference Manual, Rev. 3

Freescale Semiconductor 341

Get the latest version from freescale.com

Figure 17-6. Low-True Pulse of a Center-Aligned PWM

17.3 Register Definition

This section consists of register descriptions in address order.

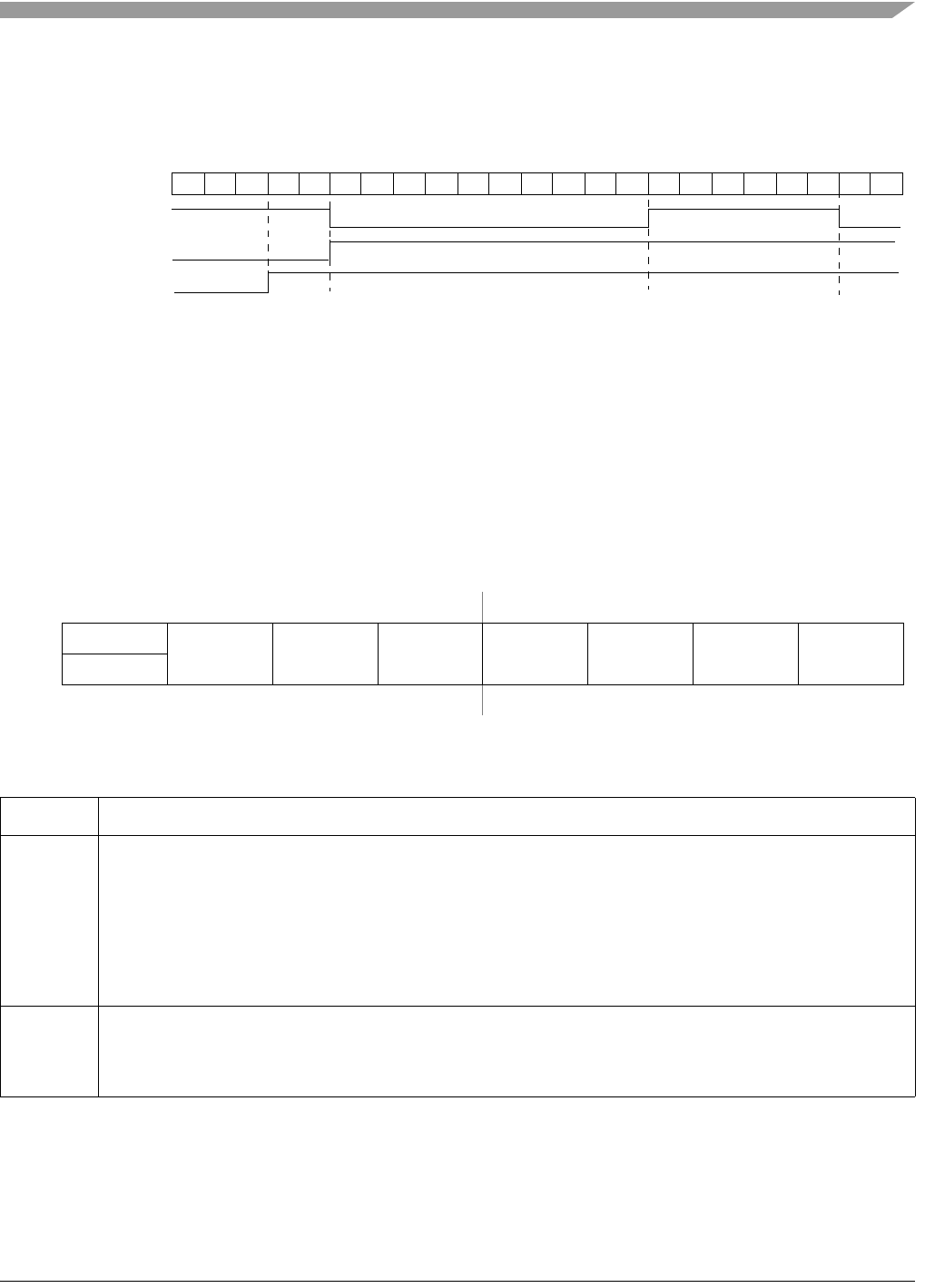

17.3.1 TPM Status and Control Register (TPMxSC)

TPMxSC contains the overflow status flag and control bits used to configure the interrupt enable, TPM

configuration, clock source, and prescale factor. These controls relate to all channels within this timer

module.

76543210

RTOF

TOIE CPWMS CLKSB CLKSA PS2 PS1 PS0

W0

Reset00000000

Figure 17-7. TPM Status and Control Register (TPMxSC)

Table 17-2. TPMxSC Field Descriptions

Field Description

7

TOF

Timer overflow flag. This read/write flag is set when the TPM counter resets to 0x0000 after reaching the modulo

value programmed in the TPM counter modulo registers. Clear TOF by reading the TPM status and control

register when TOF is set and then writing a logic 0 to TOF. If another TPM overflow occurs before the clearing

sequence is complete, the sequence is reset so TOF would remain set after the clear sequence was completed

for the earlier TOF. This is done so a TOF interrupt request cannot be lost during the clearing sequence for a

previous TOF. Reset clears TOF. Writing a logic 1 to TOF has no effect.

0 TPM counter has not reached modulo value or overflow

1 TPM counter has overflowed

6

TOIE

Timer overflow interrupt enable. This read/write bit enables TPM overflow interrupts. If TOIE is set, an interrupt is

generated when TOF equals one. Reset clears TOIE.

0 TOF interrupts inhibited (use for software polling)

1 TOF interrupts enabled

CHnF Bit

TOF Bit

...

78

765

4

321 01234567876 5...

TPMxMODH:TPMxMODL = 0x0008

TPMxMODH:TPMxMODL = 0x0005

TPMxCNTH:TPMxCNTL

TPMxCHn