MCF51QE128 MCU Series Reference Manual, Rev. 3

70 Freescale Semiconductor

Get the latest version from freescale.com

Chapter 4 Memory

4.3 RAM

The MCF51QE128/64/32 includes up to 8 Kbytes of static RAM. RAM is most efficiently accessed using

the A5-relative addressing mode (address register indirect with displacement mode). Any single bit in this

area can be accessed with the bit manipulation instructions (BCLR, BSET,etc.).

At power-on, the contents of RAM are uninitialized. RAM data is unaffected by any reset provided that

the supply voltage does not drop below the minimum value for RAM retention (V

RAM

).

4.4 Flash

The flash memory is intended primarily for program storage and read-only data. In-circuit programming

allows the operating program to be loaded into the flash memory after final assembly of the application

product. It is possible to program the entire array through the single-wire background debug interface.

Because no special voltages are needed for flash erase and programming operations, in-application

programming is also possible through other software-controlled communication paths.

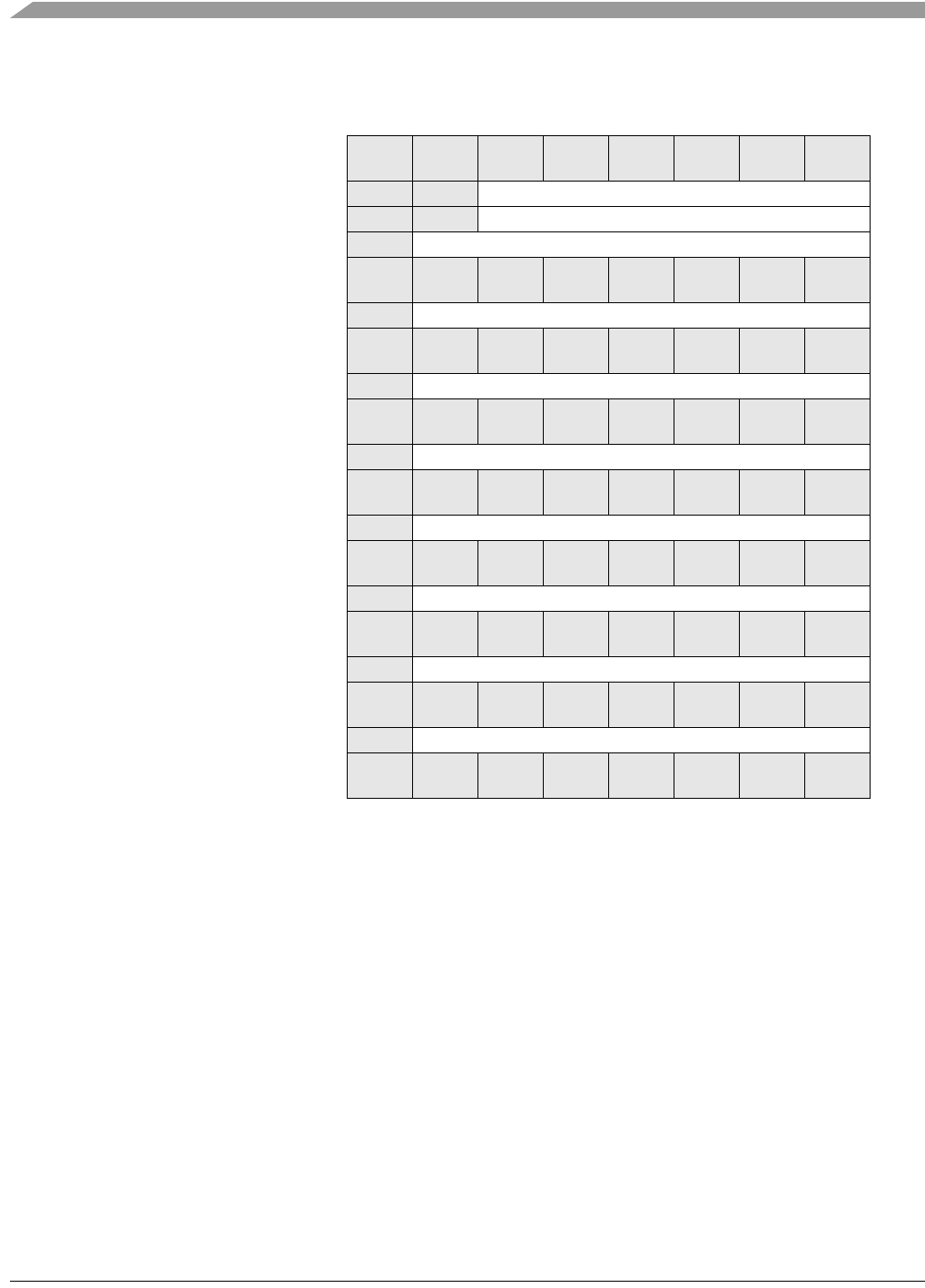

0x(FF)FF_FFDC–

0x(FF)FF_FFDD

Reserved

— — — — — — — —

0x(FF)FF_FFDE INTC_SFRC

0 0 SET

0x(FF)FF_FFDF INTC_CFRC

0 0CLR

0x(FF)FF_FFE0 INTC_SWIACK

0 VECN

0x(FF)FF_FFE1–

0x(FF)FF_FFE3

Reserved

— — — — — — — —

0x(FF)FF_FFE4 INTC_LVL1IACK

0 VECN

0x(FF)FF_FFE5–

0x(FF)FF_FFE7

Reserved

— — — — — — — —

0x(FF)FF_FFE8 INTC_LVL2IACK

0 VECN

0x(FF)FF_FFE9–

0x(FF)FF_FFEB

Reserved

— — — — — — — —

0x(FF)FF_FFEC INTC_LVL3IACK

0 VECN

0x(FF)FF_FFED–

0x(FF)FF_FFEF

Reserved

— — — — — — — —

0x(FF)FF_FFF0 INTC_LVL4IACK

0 VECN

0x(FF)FF_FFF1–

0x(FF)FF_FFF3

Reserved

— — — — — — — —

0x(FF)FF_FFF4 INTC_LVL5IACK

0 VECN

0x(FF)FF_FFF5–

0x(FF)FF_FFF7

Reserved

— — — — — — — —

0x(FF)FF_FFF8 INTC_LVL6IACK

0 VECN

0x(FF)FF_FFF9–

0x(FF)FF_FFFB

Reserved

— — — — — — — —

0x(FF)FF_FFFC INTC_LVL7IACK

0 VECN

0x(FF)FF_FFFD–

0x(FF)FF_FFFF

Reserved

— — — — — — — —

Table 4-7. V1 ColdFire Interrupt Controller Memory Map (continued)

Address Register Name msb Bit Number lsb