MCF51QE128 MCU Series Reference Manual, Rev. 3

108 Freescale Semiconductor

Get the latest version from freescale.com

Chapter 5 Resets, Interrupts, and General System Control

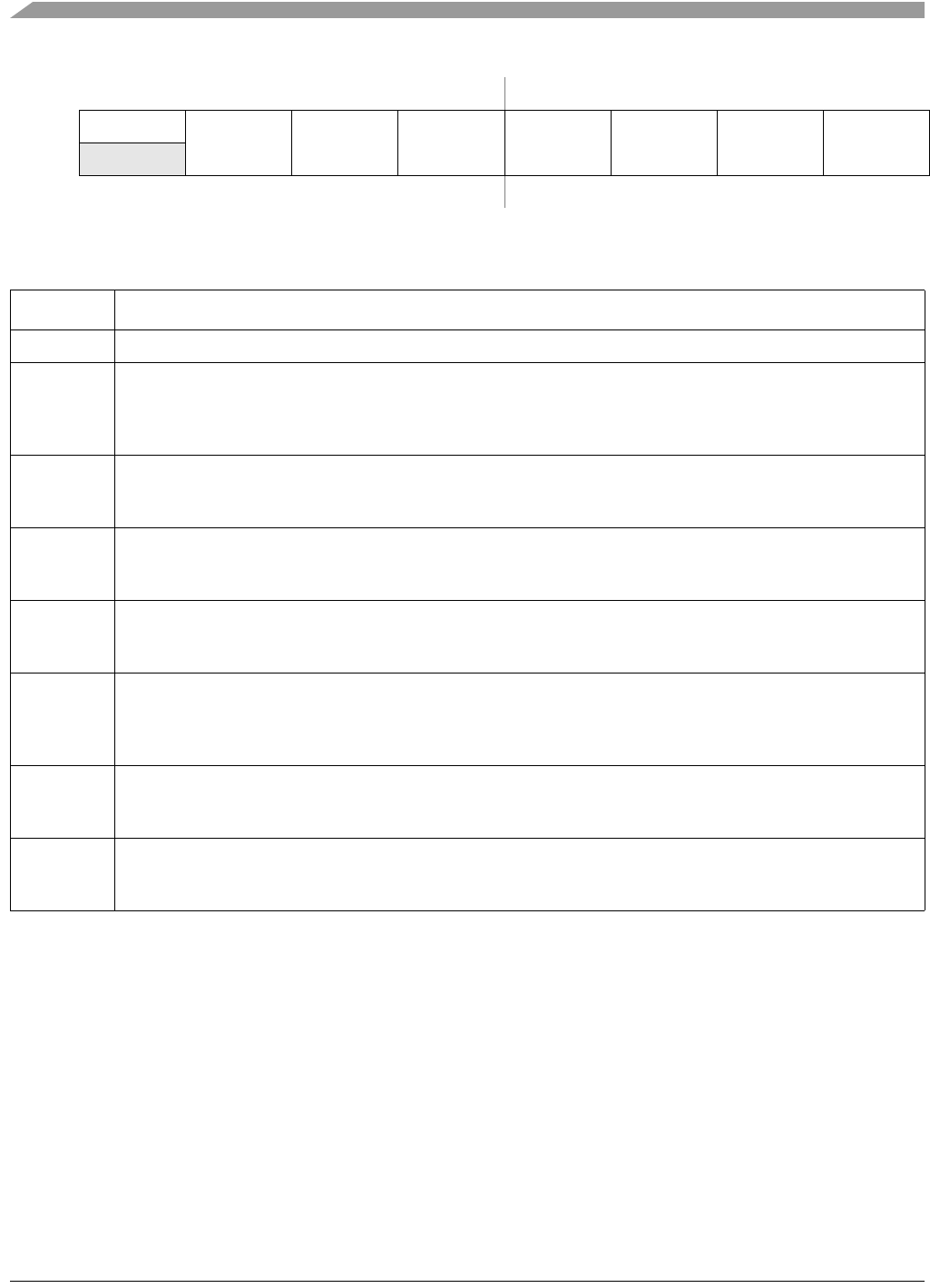

76543210

R1

FLS IRQ KBIx ACMPx RTC SPI2 SPI1

W

Reset:11111111

Figure 5-11. System Clock Gating Control 2 Register (SCGC2)

Table 5-13. SCGC2 Register Field Descriptions

Field Description

7 Reserved, must be set.

6

FLS

FTSR Clock Gate Control. This bit controls the bus clock gate to the flash registers. This bit does not affect normal

program execution from the flash array. Only the clock to the flash control registers is affected.

0 Bus clock to flash registers is disabled.

1 Bus clock to flash registers is enabled.

5

IRQ

IRQ Clock Gate Control. This bit controls the bus clock gate to the IRQ module.

0 Bus clock to the IRQ module is disabled.

1 Bus clock to the IRQ module is enabled.

4

KBIx

KBI Clock Gate Control. This bit controls the clock gate to both of the KBI modules.

0 Bus clock to the KBI modules is disabled.

1 Bus clock to the KBI modules is enabled.

3

ACMPx

ACMP Clock Gate Control. This bit controls the clock gate to both of the ACMP modules.

0 Bus clock to the ACMP modules is disabled.

1 Bus clock to the ACMP modules is enabled.

2

RTC

RTC Clock Gate Control. This bit controls the bus clock gate to the RTC module. Only the bus clock is gated; the

ICSERCLK and LPOCLK are still available to the RTC.

0 Bus clock to the RTC module is disabled.

1 Bus clock to the RTC module is enabled.

1

SPI2

SPI2 Clock Gate Control. This bit controls the clock gate to the SPI2 module.

0 Bus clock to the SPI2 module is disabled.

1 Bus clock to the SPI2 module is enabled.

0

SPI1

SPI1 Clock Gate Control. This bit controls the clock gate to the SPI1 module.

0 Bus clock to the SPI1 module is disabled.

1 Bus clock to the SPI1 module is enabled.