Analog-to-Digital Converter (S08ADC12V1)

MCF51QE128 MCU Series Reference Manual, Rev. 3

Freescale Semiconductor 225

Get the latest version from freescale.com

In 10-bit mode, the ADCCVH register holds the upper two bits of the 10-bit compare value (ADCV9 –

ADCV8). These bits are compared to the upper two bits of the result following a conversion in 10-bit mode

when the compare function is enabled.

In 8-bit mode, ADCCVH is not used during compare.

11.3.6 Compare Value Low Register (ADCCVL)

This register holds the lower 8 bits of the 12-bit or 10-bit compare value or all 8 bits of the 8-bit compare

value. Bits ADCV7:ADCV0 are compared to the lower 8 bits of the result following a conversion in 12-bit,

10-bit or 8-bit mode.

11.3.7 Configuration Register (ADCCFG)

ADCCFG selects the mode of operation, clock source, clock divide, and configure for low power or long

sample time.

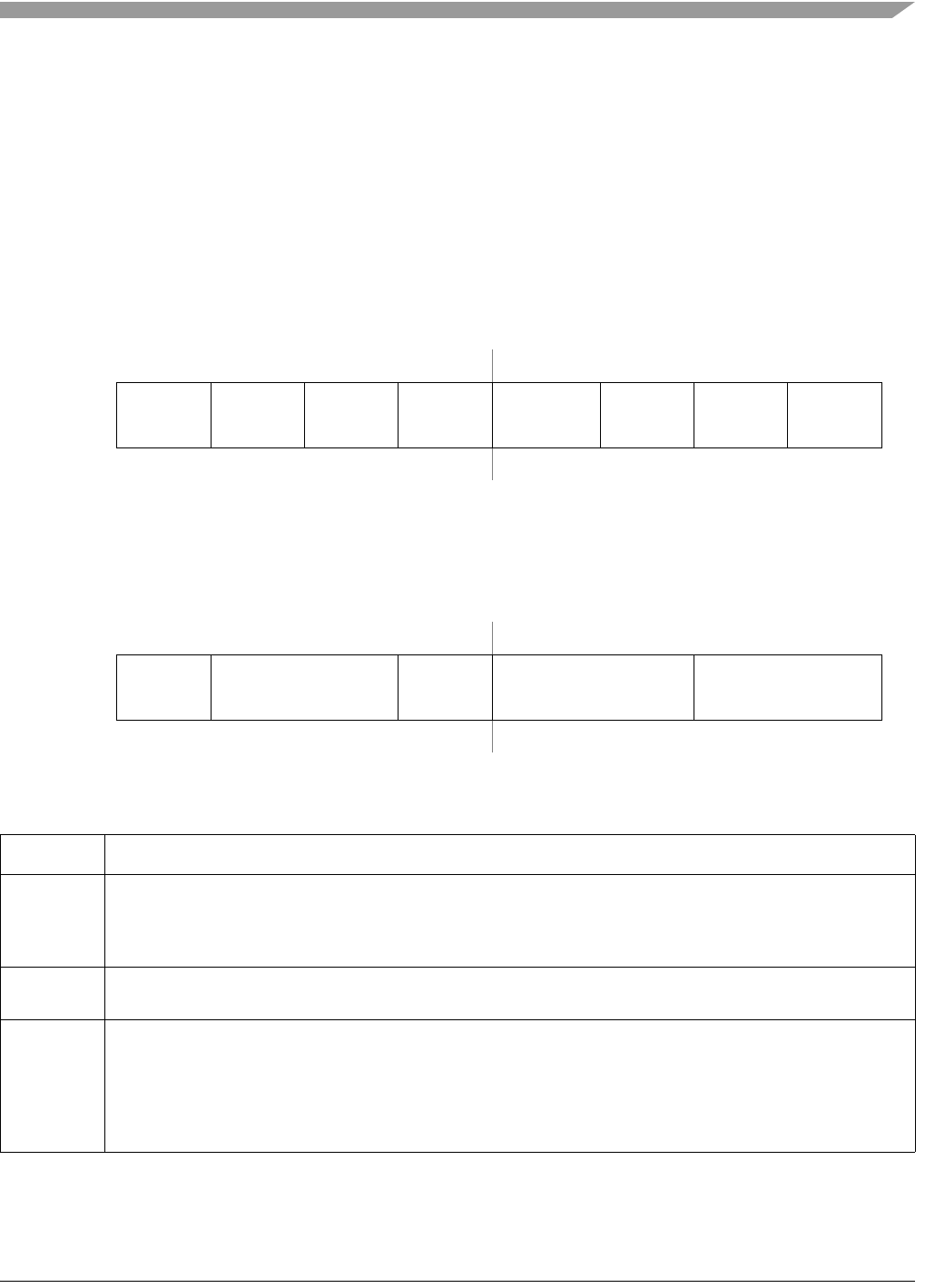

7654 3 210

R

ADCV7 ADCV6 ADCV5 ADCV4 ADCV3 ADCV2 ADCV1 ADCV0

W

Reset:0000 0 000

Figure 11-8. Compare Value Low Register(ADCCVL)

7654 3 210

R

ADLPC ADIV ADLSMP MODE ADICLK

W

Reset:0000 0 000

Figure 11-9. Configuration Register (ADCCFG)

Table 11-6. ADCCFG Register Field Descriptions

Field Description

7

ADLPC

Low-Power Configuration. ADLPC controls the speed and power configuration of the successive approximation

converter. This optimizes power consumption when higher sample rates are not required.

0 High speed configuration

1 Low power configuration:The power is reduced at the expense of maximum clock speed.

6:5

ADIV

Clock Divide Select. ADIV selects the divide ratio used by the ADC to generate the internal clock ADCK.

Ta bl e 1 1- 7 shows the available clock configurations.

4

ADLSMP

Long Sample Time Configuration. ADLSMP selects between long and short sample time. This adjusts the

sample period to allow higher impedance inputs to be accurately sampled or to maximize conversion speed for

lower impedance inputs. Longer sample times can also be used to lower overall power consumption when

continuous conversions are enabled if high conversion rates are not required.

0 Short sample time

1 Long sample time