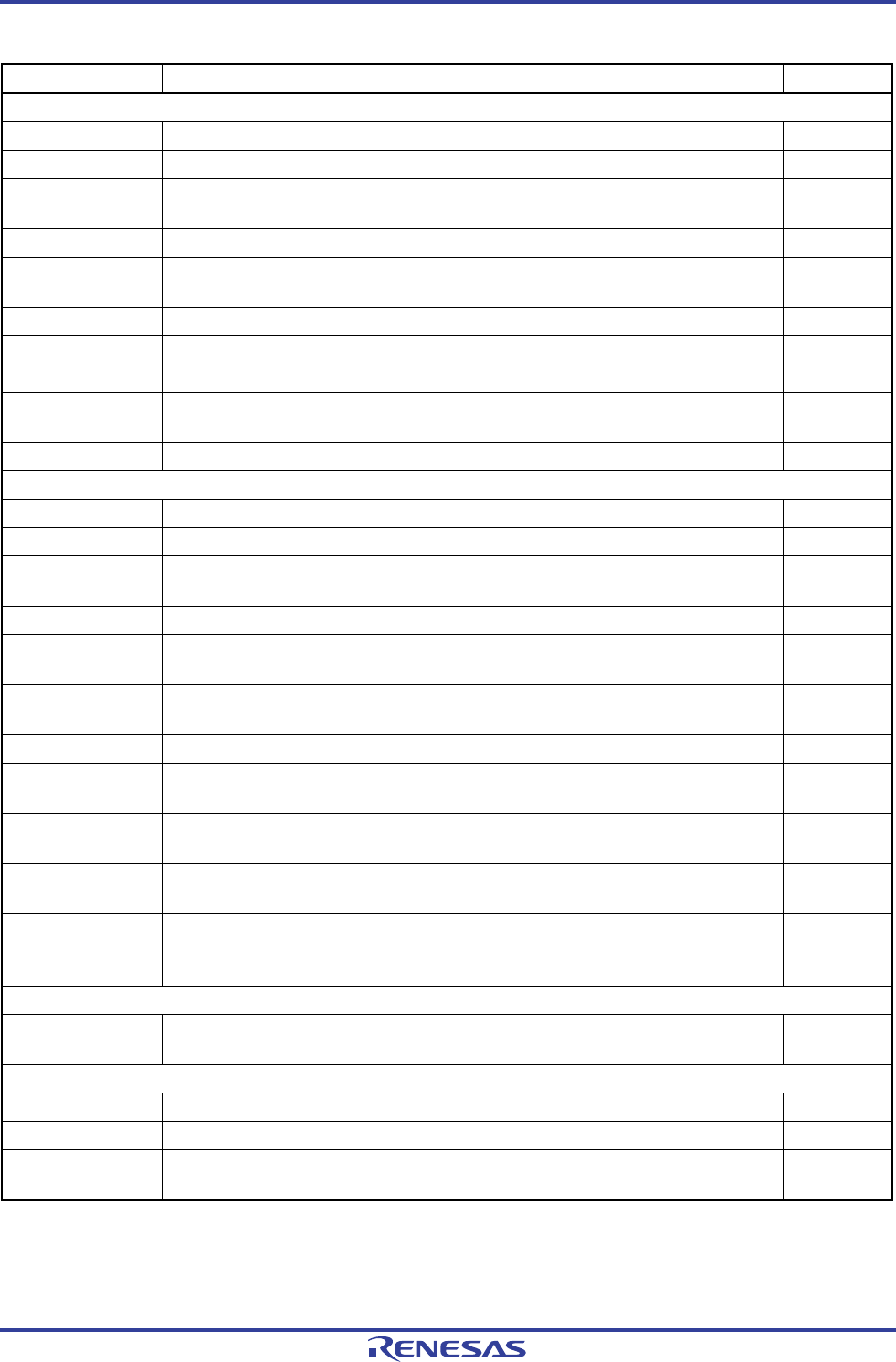

RL78/G1A APPENDIX A REVISION HISTORY

(2/5)

Page Description Classification

CHAPTER 5 CLOCK GENERATOR

p.162 Addition of description to 5.1 (1) <2> High-speed on-chip oscillator (c)

p.165 Modification of Figure 5-1. Block Diagram of Clock Generator (c)

p.167

Modification of caution 3 in Figure 5-2. Format of Clock Operation Mode Control Register

(CMC)

(c)

p.185 Modification of description in 5.4.3 High-speed on-chip oscillator (c)

p.187

Modification of Figure 5-14. Clock Generator Operation When Power Supply Voltage Is

Turned On

(c)

p.188 Modification of description in 5.6.1 Example of setting high-speed on-chip oscillator (c)

p.189 Modification of description in 5.6.2 Example of setting X1 oscillation clock (c)

p.191 Modification of Figure 5-15. CPU Clock Status Transition Diagram (c)

p.194

Modification of description in Table 5-3. CPU Clock Transition and SFR Register Setting

Examples

(c)

p.202 to 204 Addition of note and modification of remark in 5.7 (1) X1 oscillation: (c)

CHAPTER 6 TIMER ARRAY UNIT

p.214 to 216 Modification of Figures 6-2 to 6-6 (c)

p.239 Modification of note in 6.3.14 Noise filter enable register 1 (NFEN1) (c)

p.251

Modification of Figure 6-29. Operation Timing (In Capture Mode : Input Pulse Interval

Measurement)

(c)

p.263, 264 Addition of 6.7 Timer Input (TImn) Cntorol (c)

p.296

Modification of description and addition of note to Figure 6-69. Example of Set Contents of

Registers When One-Shot Pulse Output Function Is Used (Master Channel)

(c)

p.297

Modification of description and note in Figure 6-70. Example of Set Contents of Registers

When One-Shot Pulse Output Function Is Used (Slave Channel)

(c)

p.299 Modification of Figure 6-71. Operation Procedure of One-Shot Pulse Output Function (c)

p.303

Addition of note to Figure 6-74. Example of Set Contents of Registers When PWM

Function (Master Channel) Is Used

(c)

p.304

Modification of description and note in Figure 6-75. Example of Set Contents of Registers

When PWM Function (Slave Channel) Is Used

(c)

p.311

Addition note to Figure 6-79. Example of Set Contents of Registers When Multiple PWM

Output Function (Master Channel) Is Used

(c)

p.312

Modification of description and note in Figure 6-80. Example of Set Contents of Registers

When Multiple PWM Output Function (Slave Channel) Is Used (output two types of

PWMs)

(c)

CHAPTER 7 REAL-TIME CLOCK

p.336

Modification of Figure 7-23. Operation when (DEV, F6, F5, F4, F3, F2, F1, F0) = (1, 1, 1, 0,

1, 1, 1, 0)

(c)

CHAPTER 8 12-BIT INTERVAL TIMER

p.343 Modification of Figure 8-2. Format of Peripheral Enable Register 0 (PER0) (c)

p.344 Modification of description in 8.3.2 Operation speed mode control register (OSMC) (c)

p.346

Modification of Figure 8-5. 12-bit Interval Timer Operation Timing (ITCMP11 to ITCMP0 =

0FFH, count clock: f

SUB = 32.768 kHz)

(c)

Remark “Classification” in the above table classifies revisions as follows.

(a): Error correction, (b): Addition/change of specifications, (c): Addition/change of description or note,

(d): Addition/change of package, part number, or management division, (e): Addition/change of related

documents

R01UH0305EJ0200 Rev.2.00 970

Jul 04, 2013