RL78/G1A CHAPTER 17 KEY INTERRUPT FUNCTION

17.3.4 Port mode registers 0 to 2, 7, 12, 15 (PM0 to PM2, PM7, PM12, PM15)

<R>

When using P70/KR0 to P77/KR7, P05/KR8, P06/KR9, P00/(KR0) to P04/(KR4), P22/(KR5) to P26/(KR9), P10/(KR0)

to P15/(KR5), P120/(KR0), P151/(KR6) to P154/(KR9) as a key input, set the bits corresponding to port mode registers 0

to 2, 7, 12, 15 (PM0 to PM2, PM7, PM12, PM15) to 1. At this time, the output latch of the bits corresponding to port

registers 0 to 2, 7, 12, 15 (P0 to P2, P7, P12, P15) may be 0 or 1.

The PM0 to PM2, PM7, PM12, PM15 registers can be set by a 1-bit or 8-bit memory manipulation instruction. Reset

signal generation sets these registers to FFH.

In addition, use of an on-chip pull-up resistor can be specified in 1-bit units by pull-up resistor option registers 0, 1, 7, 12

(PU0, PU1, PU7, PU12).

Remark Functions in parentheses can be assigned via settings in the peripheral I/O redirection register (PIOR)

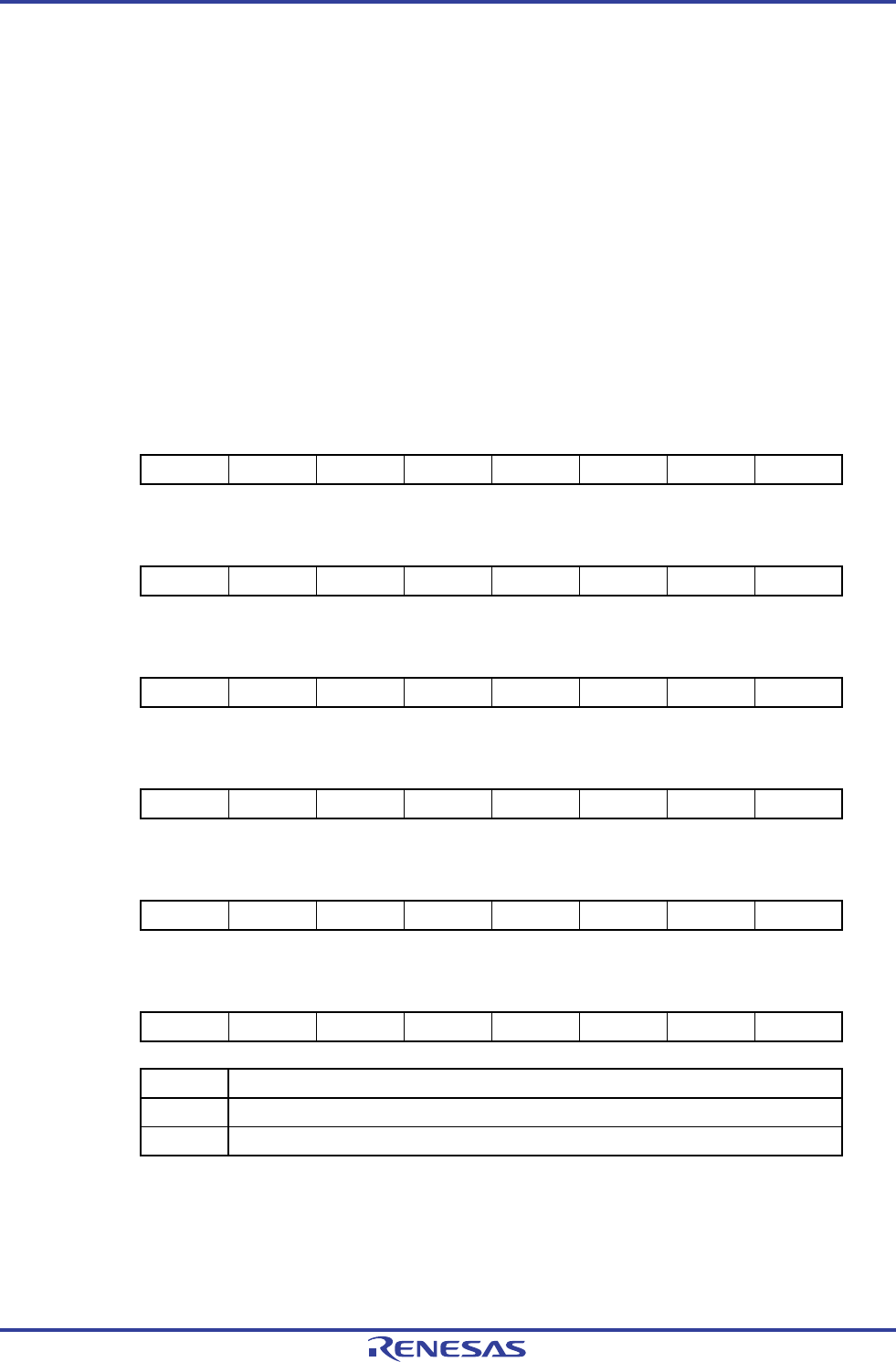

Figure 17-5. Format of Port Mode Register 0 to 2, 7, 12, 15 (PM0 to PM2, PM7, PM12, PM15)

Address: FFF20H After reset: FFH R/W

Symbol 7 6 5 4 3 2 1 0

PM0 1 PM06 PM05 PM04 PM03 PM02 PM01 PM00

Address: FFF21H After reset: FFH R/W

Symbol 7 6 5 4 3 2 1 0

PM1 1 PM16 PM15 PM14 PM13 PM12 PM11 PM10

Address: FFF22H After reset: FFH R/W

Symbol 7 6 5 4 3 2 1 0

PM2 PM27 PM26 PM25 PM24 PM23 PM22 PM21 PM20

Address: FFF27H After reset: FFH R/W

Symbol 7 6 5 4 3 2 1 0

PM7 PM77 PM76 PM75 PM74 PM73 PM72 PM71 PM70

Address: FFF2CH After reset: FFH R/W

Symbol 7 6 5 4 3 2 1 0

PM12 1 1 1 1 1 1 1 PM120

Address: FFF2FH After reset: FFH R/W

Symbol 7 6 5 4 3 2 1 0

PM15 1 1 1 PM154 PM153 PM152 PM151 PM150

PMmn I/O mode selection for Pmn/KRk pin (m = 0 to 2, 7, 12, 15, n = 0 to 7, k = 0 to 9)

0 Output mode (output buffer on)

1 Input mode (output buffer off)

R01UH0305EJ0200 Rev.2.00 720

Jul 04, 2013