RL78/G1A CHAPTER 6 TIMER ARRAY UNIT

R01UH0305EJ0200 Rev.2.00 204

Jul 04, 2013

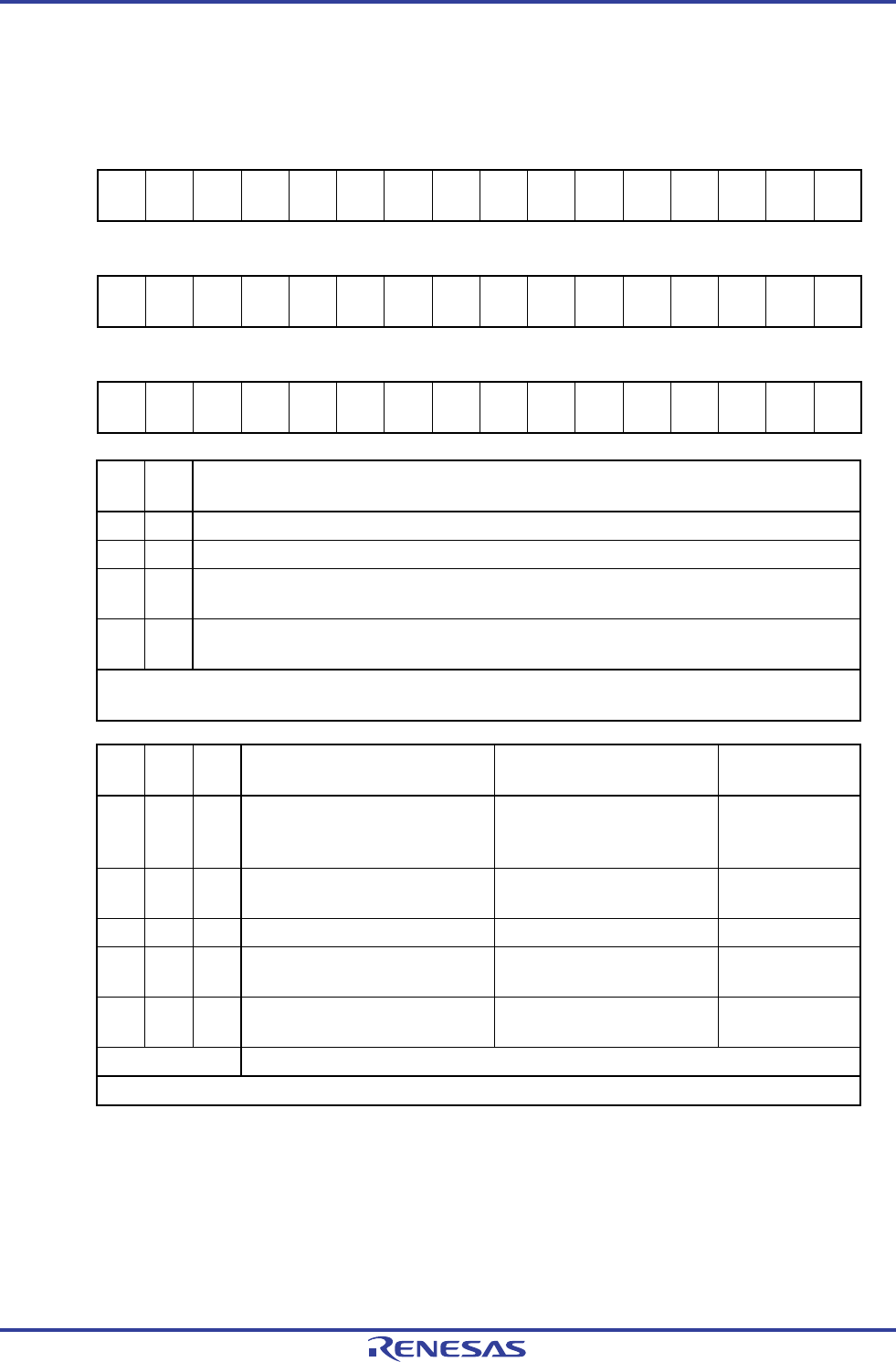

Figure 6-11. Format of Timer Mode Register mn (TMRmn) (3/4)

Address: F0190H, F0191H (TMR00) to F019EH, F019FH (TMR07) After reset: 0000H R/W

Symbol 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

TMRmn

(n = 2, 4, 6 )

CKS

mn1

CKS

mn0

0

CCS

mn

MAST

ERmn

STS

mn2

STS

mn1

STS

mn0

CIS

mn1

CIS

mn0

0 0

MD

mn3

MD

mn2

MD

mn1

MD

mn0

Symbol 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

TMRmn

(n = 1, 3)

CKS

mn1

CKS

mn0

0

CCS

mn

SPLIT

mn

STS

mn2

STS

mn1

STS

mn0

CIS

mn1

CIS

mn0

0 0

MD

mn3

MD

mn2

MD

mn1

MD

mn0

Symbol 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

TMRmn

(n = 0, 5, 7)

CKS

mn1

CKS

mn0

0

CCS

mn

0

Note

STS

mn2

STS

mn1

STS

mn0

CIS

mn1

CIS

mn0

0 0

MD

mn3

MD

mn2

MD

mn1

MD

mn0

CIS

mn1

CIS

mn0

Selection of TImn pin input valid edge

0 0 Falling edge

0 1 Rising edge

1 0

Both edges (when low-level width is measured)

Start trigger: Falling edge, Capture trigger: Rising edge

1 1

Both edges (when high-level width is measured)

Start trigger: Rising edge, Capture trigger: Falling edge

If both the edges are specified when the value of the STSmn2 to STSmn0 bits is other than 010B, set the CISmn1

to CISmn0 bits to 10B.

MD

mn3

MD

mn2

MD

mn1

Operation mode of channel n Corresponding function

Count operation of

TCR

0 0 0 Interval timer mode

Interval timer / Square wave

output / Divider function / PWM

output (master)

Counting down

0 1 0 Capture mode

Input pulse interval

measurement

Counting up

0 1 1 Event counter mode External event counter Counting down

1 0 0 One-count mode

Delay counter / One-shot pulse

output / PWM output (slave)

Counting down

1 1 0 Capture & one-count mode

Measurement of high-/low-level

width of input signal

Counting up

Other than above Setting prohibited

The operation of each mode varies depending on MDmn0 bit (see next table).

Note Bit 11 is fixed at 0 of read only, write is ignored.

Remark m: Unit number (m = 0), n: Channel number (n = 0 to 7 (however, timer input pin (TImn), timer output pin

(TOmn) : n = 0, 1, 3 to 7))