RL78/G1A CHAPTER 6 TIMER ARRAY UNIT

R01UH0305EJ0200 Rev.2.00 224

Jul 04, 2013

6.5.2 Start timing of counter

Operation of timer count register mn (TCRmn) is enabled by setting of TSmn bit of timer channel start register m (TSm).

Operation from when counting is enabled to when timer count register mn (TCRmn) starts counting is shown in Table 6-6.

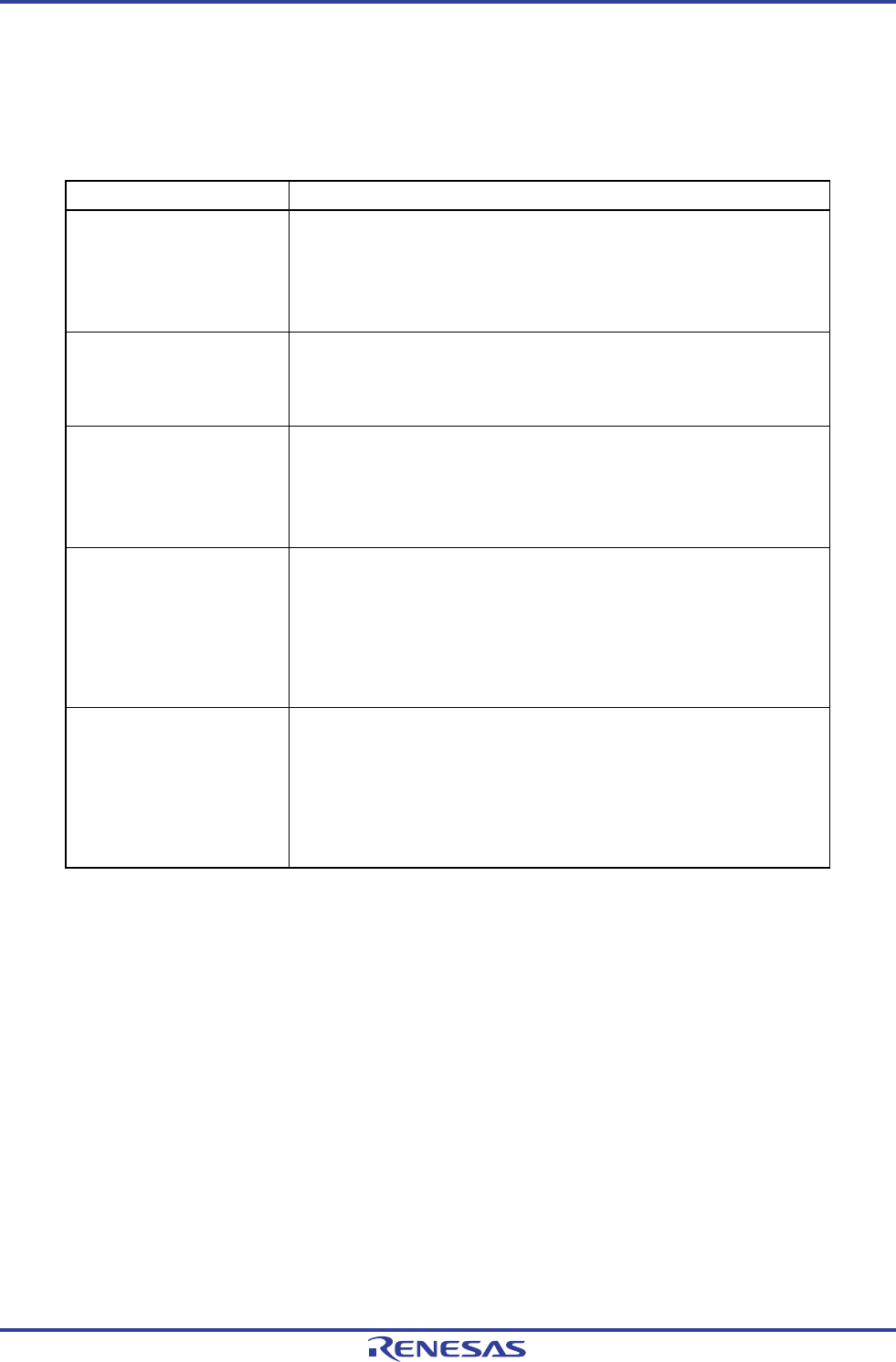

Table 6-6. Operations from Count Operation Enabled State to Timer count Register mn (TCRmn) Count Start

Timer operation mode Operation when TSmn = 1 is set

• Interval timer mode

No operation is carried out from start trigger detection (TSmn=1) until count clock

generation.

The first count clock loads the value of the TDRmn register to the TCRmn

register and the subsequent count clock performs count down operation (see

6.5.3 (1) Operation of interval timer mode).

• Event counter mode

Writing 1 to the TSmn bit loads the value of the TDRmn register to the TCRmn

register.

If detect edge of TImn input. The subsequent count clock performs count down

operation (see 6.5.3 (2) Operation of event counter mode).

• Capture mode

No operation is carried out from start trigger detection (TSmn = 1) until count

clock generation.

The first count clock loads 0000H to the TCRmn register and the subsequent

count clock performs count up operation (see 6.5.3 (3) Operation of capture

mode (input pulse interval measurement)).

• One-count mode

The waiting-for-start-trigger state is entered by writing 1 to the TSmn bit while the

timer is stopped (TEmn = 0).

No operation is carried out from start trigger detection until count clock

generation.

The first count clock loads the value of the TDRmn register to the TCRmn

register and the subsequent count clock performs count down operation (see

6.5.3 (4) Operation of one-count mode).

• Capture & one-count mode

The waiting-for-start-trigger state is entered by writing 1 to the TSmn bit while the

timer is stopped (TEmn = 0).

No operation is carried out from start trigger detection until count clock

generation.

The first count clock loads 0000H to the TCRmn register and the subsequent

count clock performs count up operation (see 6.5.3 (5) Operation of capture &

one-count mode (high-level interval measurement)).