RL78/G1A CHAPTER 3 CPU ARCHITECTURE

R01UH0305EJ0200 Rev.2.00 78

Jul 04, 2013

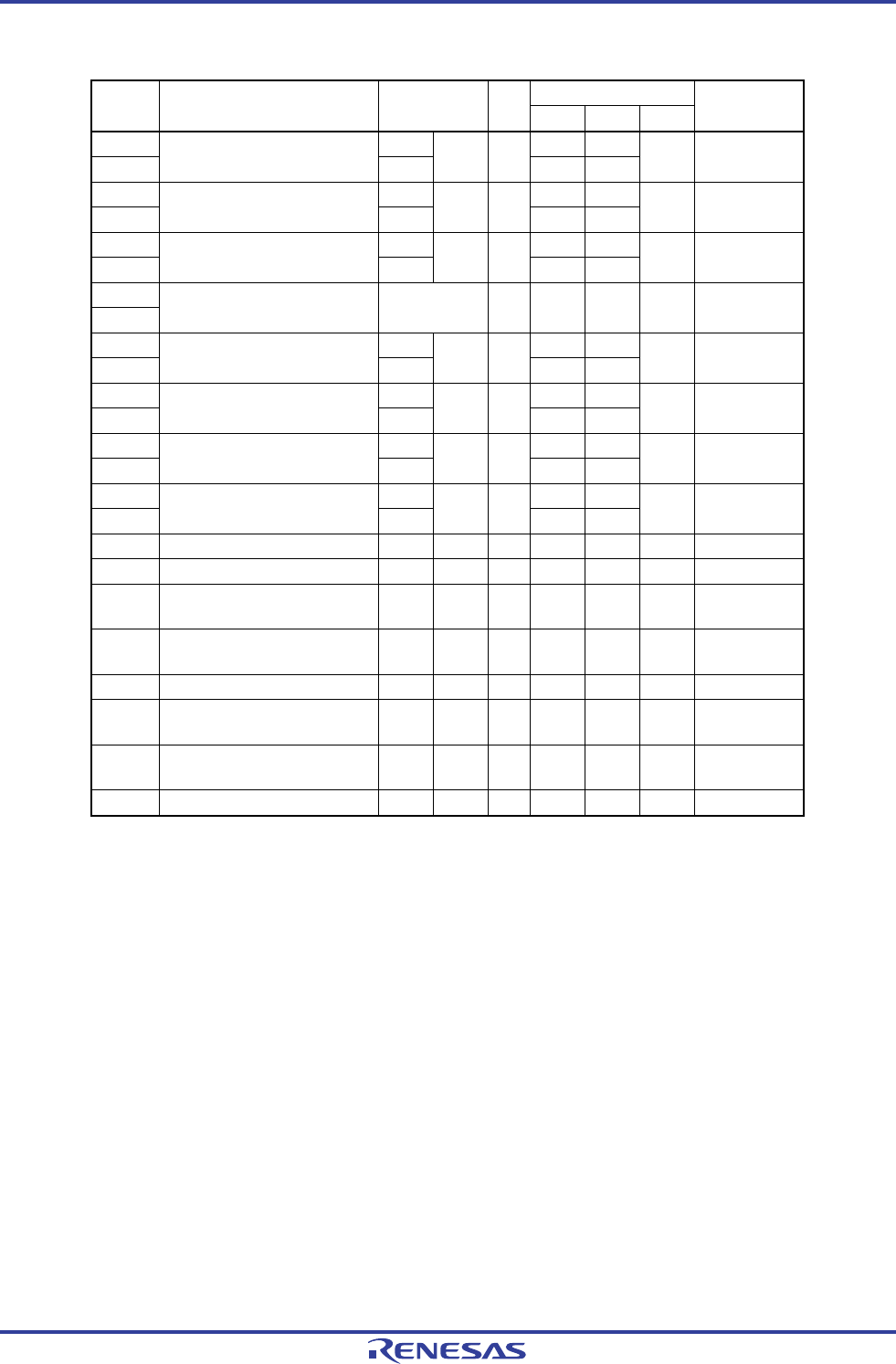

Table 3-6. Extended SFR (2nd SFR) List (6/6)

Manipulable Bit Range Address

Special Function Register (SFR) Name

Symbol R/W

1-bit 8-bit 16-bit

After Reset

F01B0H TE0L

√ √

F01B1H

Timer channel enable status

register 0

−

TE0 R

− −

√

0000H

F01B2H TS0L

√ √

F01B3H

Timer channel start register 0

−

TS0 R/W

− −

√

0000H

F01B4H TT0L

√ √

F01B5H

Timer channel stop register 0

−

TT0 R/W

− −

√

0000H

F01B6H

F01B7H

Timer clock select register 0 TPS0 R/W

− − √

0000H

F01B8H TO0L

− √

F01B9H

Timer output register 0

−

TO0 R/W

− −

√

0000H

F01BAH TOE0L

√ √

F01BBH

Timer output enable register 0

−

TOE0 R/W

− −

√

0000H

F01BCH TOL0L

− √

F01BDH

Timer output level register 0

−

TOL0 R/W

− −

√

0000H

F01BEH TOM0L

− √

F01BFH

Timer output mode register 0

−

TOM0 R/W

− −

√

0000H

F0230H IICA control register 00

IICCTL00

R/W

√ √ −

00H F0230H

F0231H IICA control register 01

IICCTL01

R/W

√ √ −

00H F0231H

F0232H IICA low-level width setting

register 0

IICWL0 R/W

− √ −

FFH F0232H

F0233H IICA high-level width setting

register 0

IICWH0 R/W

− √ −

FFH F0233H

F0234H Slave address register 0 SVA0 R/W

− √ −

00H F0234H

F02F0H Flash memory CRC control

register

CRC0

CTL

R/W

√ √ −

00H F02F0H

F02F2H Flash memory CRC operation

result register

PGCR

CL

R/W

− − √

0000H F02F2H

F02FAH CRC data register CRCD R/W

− − √

0000H F02FAH

Remark For SFRs in the SFR area, see Table 3-5 SFR List.