RL78/G1A CHAPTER 12 SERIAL ARRAY UNIT

R01UH0305EJ0200 Rev.2.00 560

Jul 04, 2013

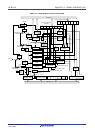

(2) Processing flow

Figure 12-111. Timing Chart of Data Reception

(a) When starting data reception

D7 D6 D5 D4 D3 D2 D1 D0

SSmn

SEmn

SOEmn

SDRmn

SCLr output

SDAr output

SDAr input

Shift

register mn

INTIICr

TSFmn

ACK

STmn

TXEmn = 0 / RXEmn = 1

TXEmn,

RXEmn

TXEmn = 1 / RXEmn = 0

Shift operation

“H”

Dummy data (FFH)

Receive data

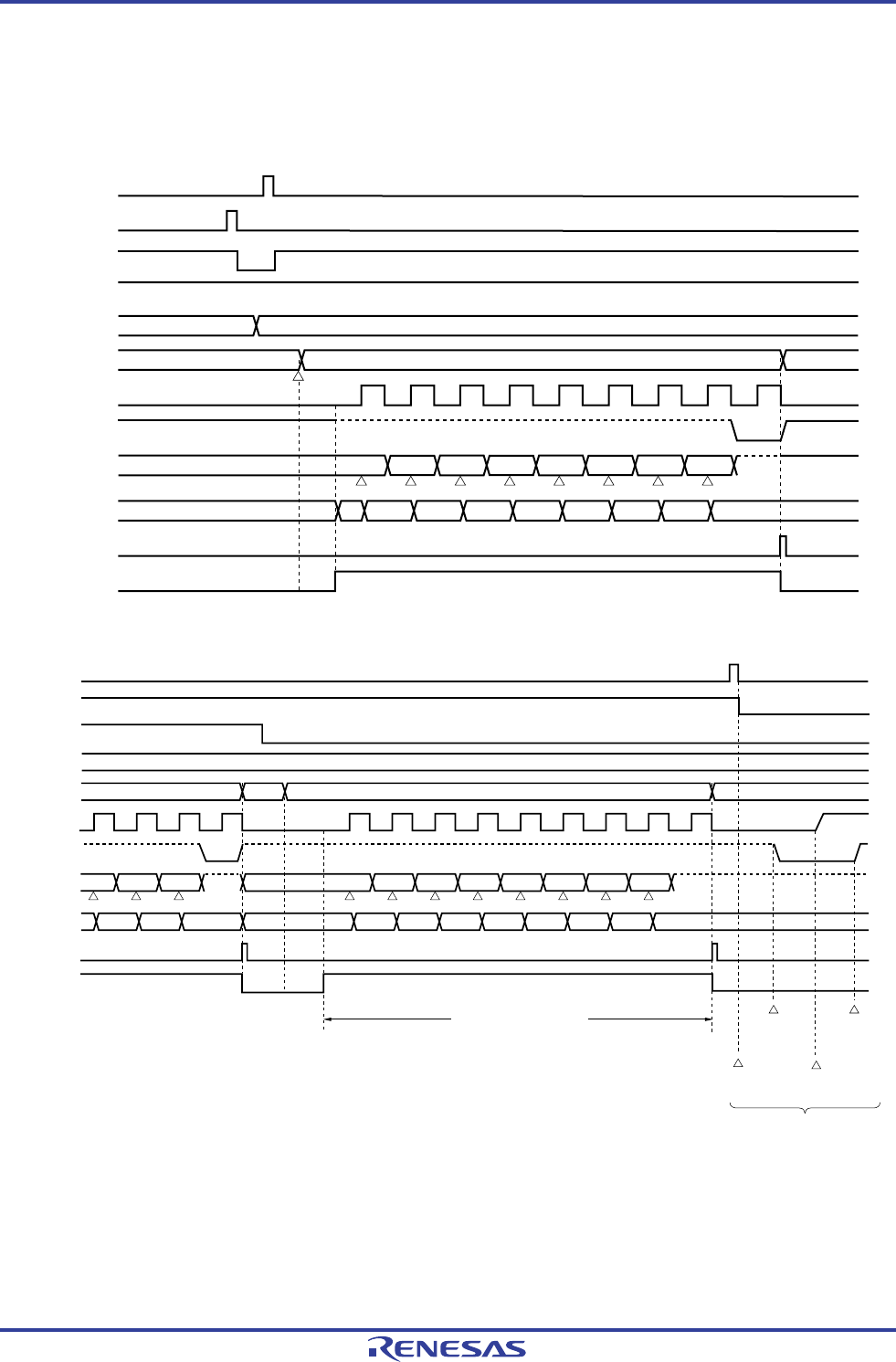

(b) When receiving last data

D7 D6 D5 D4 D3 D2 D1 D0D2 D1 D0

STmn

SEmn

SOEmn

SDRmn

SCLr output

SDAr output

SDAr input

Shift

register mn

INTIICr

TSFmn

Receive data

Receive data

Output is enabled by serial

communication operation

Output is stopped by serial communication operation

NACKACK

TXEmn = 0 / RXEmn = 1

TXEmn,

RXEmn

Step condition

Reception of last byte

IIC operation stop

SOmn bit

manipulation

CKOmn bit

manipulation

SOmn bit

manipulation

Shift operation

Dummy data (FFH)

Shift operation

Dummy data (FFH)

Remark m: Unit number (m = 0, 1), n: Channel number (n = 0 to 3), r: IIC number (r = 00, 01, 10, 11, 20, 21),

mn = 00 to 03, 10, 11