RL78/G1A CHAPTER 1 OUTLINE

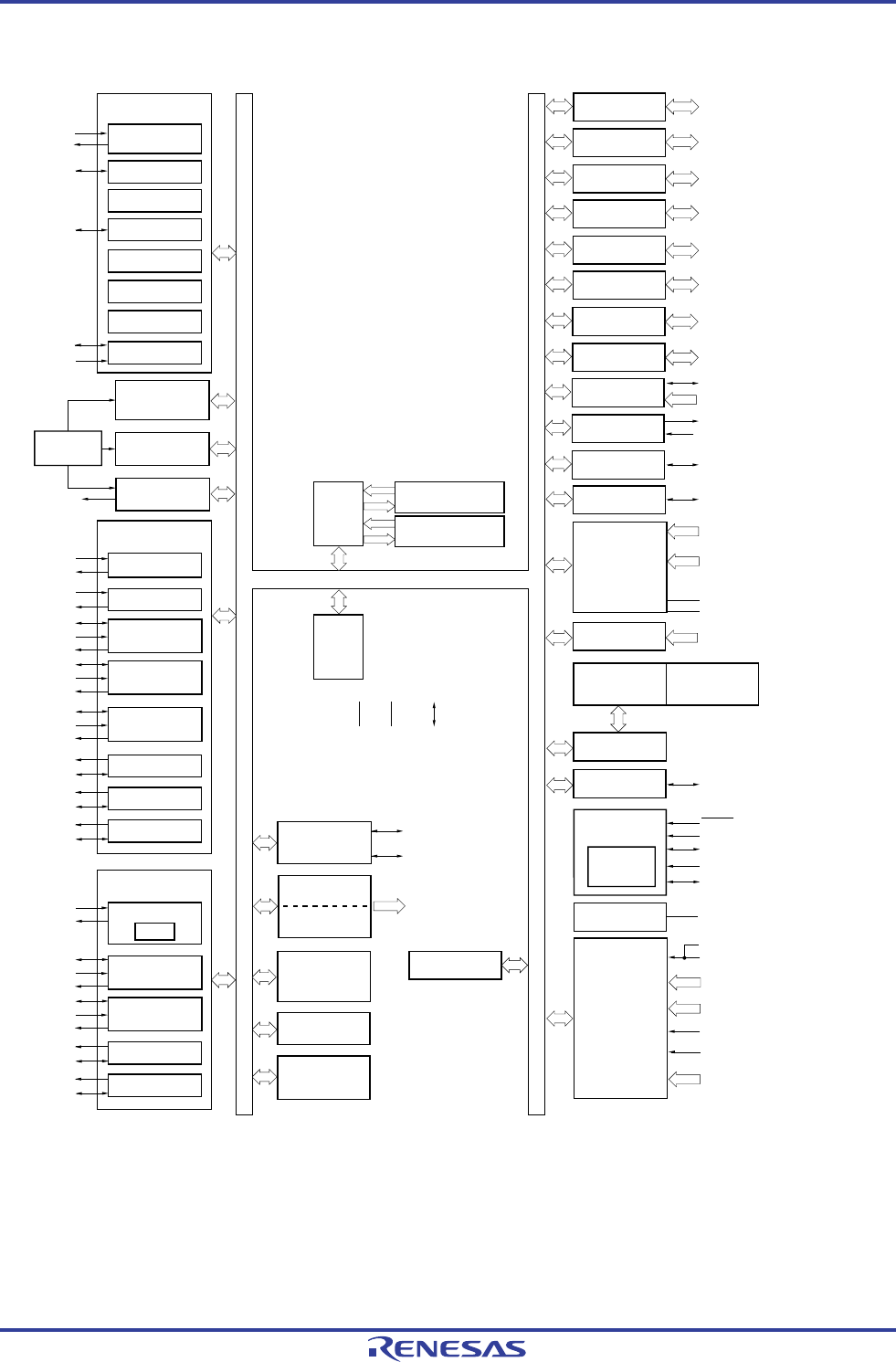

1.5.3 48-pin products

<R>

VOLTAGE

REGULATOR

REGC

INTERRUPT

CONTROL

RAM

WINDOW

WATCHDOG

TIMER

POWER ON RESET/

VOLTAGE

DETECTOR

POR/LVD

CONTROL

RESET CONTROL

SYSTEM

CONTROL

RESET

X1/P121

X2/EXCLK/P122

HIGH-SPEED

ON-CHIP

OSCILLATOR

ON-CHIP DEBUG

TOOL0/P40

SERIAL ARRAY

UNIT0 (4ch)

UART0

UART1

IIC00

RxD0/P11

TxD0/P12

RxD1/P03

TxD1/P02

SCL00/P10

SDA00/P11

TIMER ARRAY

UNIT (8ch)

ch2

TI03/TO03/P31

ch3

ch0

ch1

ch4

ch5

ch6

ch7

INTP8/P74,

INTP9/P75

2

INTP0/P137

INTP3/P30,

INTP4/P31

INTP6/P140

INTP1/P50,

INTP2/P51

RxD2/P14

A/D CONVERTER

9

ANI0/P20 to ANI7/P2, ANI8/P150

AV

REFP

/P20

AV

REFM

/P21

CSI11

SCK11/P30

SO11/P51

SI11/P50

IIC01

SCL01/P75

SDA01/P74

IIC11

SCL11/P30

SDA11/P50

TI07/TO07/P41

TI00/P02

TO00/P03

BCD

ADJUSTMENT

SCK00/P10

SO00/P12

SI00/P11

CSI00

V

SS

,

AV

SS

TOOLRxD/P11,

TOOLTxD/P12

V

DD

,

AV

DD

SERIAL

INTERFACE IICA0

SDAA0/P61

SCLA0/P60

2

2

INTP5/P16

MULTIPLIER&

DIVIDER,

MULITIPLY-

ACCUMULATOR

XT1/P123

XT2/EXCLKS/P124

PORT 0

P02, P03

2

BUZZER OUTPUT

PCLBUZ0/P140,

PCLBUZ1/P15

CLOCK OUTPUT

CONTROL

KEY RETURN

6(6)

KR0/P70 to KR5/P75

(KR0/P10 to KR5/P15)

(KR0/P02, KR1/P03, KR2/P22 to KR5/P25)

15

ANI16/P03, ANI17/P02, ANI18/P147,

ANI19/P120, ANI20/P11 to ANI24/P15,

ANI25, P51, ANI26/P50, P30/ANI27,

ANI28/P70, ANI29/P31, ANI30/P41

SCK01/P75

SO01/P73

SI01/P74

CSI01

SERIAL ARRAY

UNIT1 (2ch)

UART2

LINSEL

IIC20

RxD2/P14

TxD2/P13

SCL20/P15

SDA20/P14

IIC21

SCL21/P70

SDA21/P71

SCK20/P15

SO20/P13

SI20/P14

CSI20

SCK21/P70

SO21/P72

SI21/P71

CSI21

DIRECT MEMORY

ACCESS

CONTROL

PORT 15

2

TI01/TO01/P16

RTC1HZ/P30

RxD2/P14

REAL-TIME

CLOCK

RL78

CPU

CORE

CODE FLASH MEMORY

DATA FLASH MEMORY

INTERVAL

TIMER

PORT 1

P10 to P16

PORT 2

P20 to P27

8

PORT 3

P30, P31

2

PORT 4

PORT 5

7

PORT 12

P121 to P124

P40, P41

2

P50, P51

2

4

P120

PORT 13

P130

P137

PORT 6

PORT 7

P70 to P75

6

P60 to P63

4

PORT 14 P140

P150

LOW-SPEED

ON-CHIP

OSCILLATOR

CRC

Remark Functions in parentheses in the above figure can be assigned via settings in the peripheral I/O redirection

register (PIOR). See Figure 4-8 Format of Peripheral I/O Redirection Register (PIOR).

R01UH0305EJ0200 Rev.2.00 15

Jul 04, 2013