RL78/G1A CHAPTER 11 A/D CONVERTER

R01UH0305EJ0200 Rev.2.00 377

Jul 04, 2013

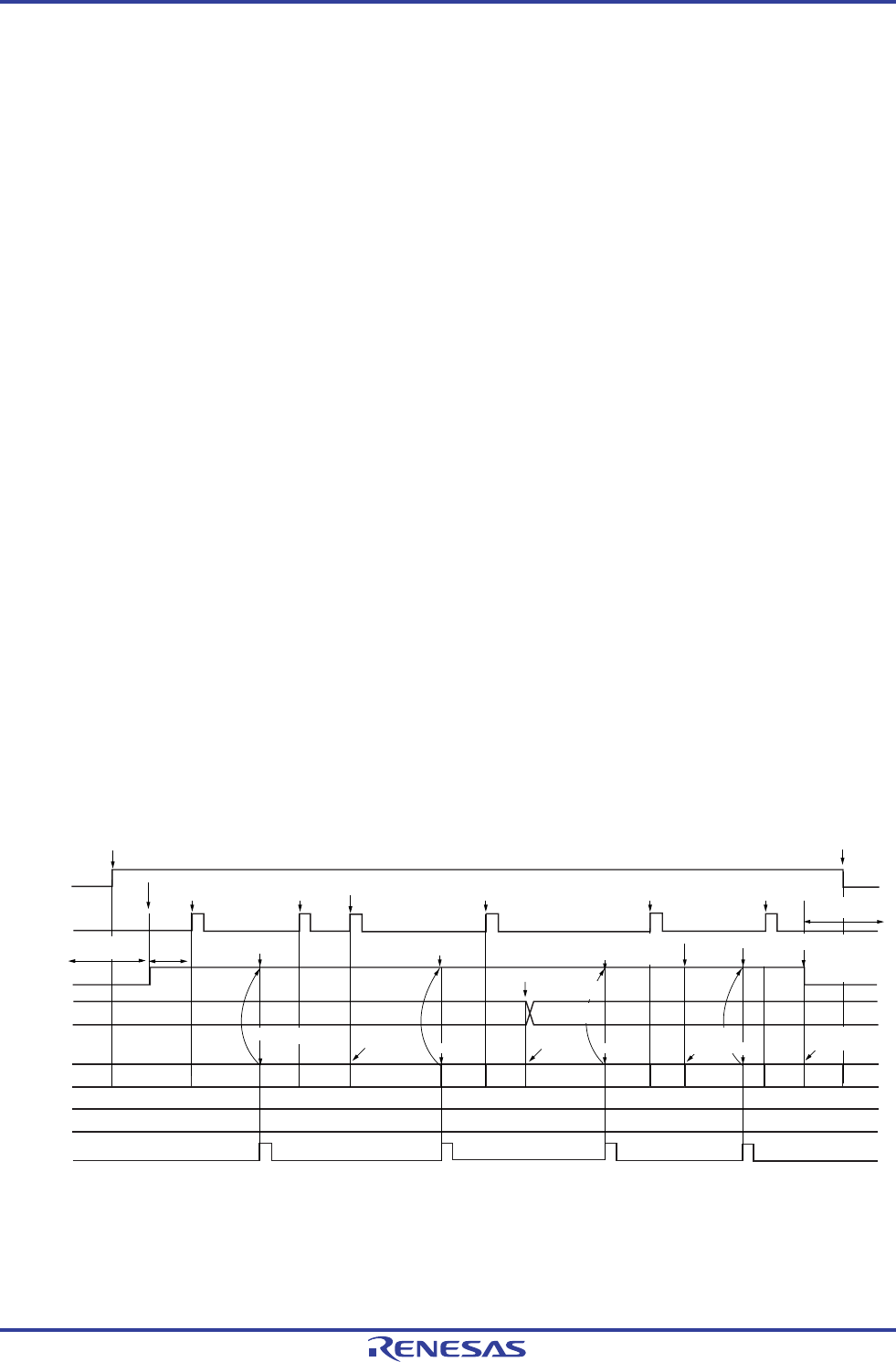

11.6.6 Hardware trigger no-wait mode (select mode, one-shot conversion mode)

<1> In the stop status, the ADCE bit of A/D converter mode register 0 (ADM0) is set to 1, and the system enters the

A/D conversion standby status.

<2> After the software counts up to the stabilization wait time

Note

, the ADCS bit of the ADM0 register is set to 1 to

place the system in the hardware trigger standby status (and conversion does not start at this stage). Note that,

while in this status, A/D conversion does not start even if ADCS is set to 1.

<3> If a hardware trigger is input while ADCS = 1, A/D conversion is performed on the analog input specified by the

analog input channel specification register (ADS).

<4> When A/D conversion ends, the conversion result is stored in the A/D conversion result register (ADCR, ADCRH),

and the A/D conversion end interrupt request signal (INTAD) is generated.

<5> After A/D conversion ends, the ADCS bit remains set to 1, and the system enters the A/D conversion standby

status.

<6> If a hardware trigger is input during conversion operation, the current A/D conversion is interrupted, and

conversion restarts. The partially converted data is discarded.

<7> When the value of the ADS register is rewritten or overwritten during conversion operation, the current A/D

conversion is interrupted, and A/D conversion is performed on the analog input respecified by the ADS register.

The partially converted data is discarded.

<8> When ADCS is overwritten with 1 during conversion operation, the current A/D conversion is interrupted, and

conversion restarts. The partially converted data is discarded.

<9> When ADCS is cleared to 0 during conversion operation, the current A/D conversion is interrupted, and the

system enters the A/D conversion standby status. However, the A/D converter does not stop in this status.

<10> When ADCE is cleared to 0 while in the A/D conversion standby status, the A/D converter enters the stop status.

When ADCS = 0, inputting a hardware trigger is ignored and A/D conversion does not start.

Note If a high-accuracy channel is selected as the analog input channel: Stabilization wait time = 0.5

μ

s

If a standard channel is selected as the analog input channel: Stabilization wait time = 2

μ

s

Figure 11-22. Example of Hardware Trigger No-Wait Mode (Select Mode, One-Shot Conversion Mode)

Operation Timing

ADCE

ADCS

ADS

INTAD

ADCR,

ADCRH

A/D

conversion

status

Hardware

trigger

ADCE is set to 1.

<1>

Stop

status

Stop

status

Conversion

standby

ANI0

Data 1

(ANI0)

Data 1

(ANI0)

Data 3

(ANI0)

Data 5

(ANI1)

Data 7

(ANI1)

Data 2

(ANI0)

Data 5

(ANI1)

Data 7

(ANI1)

Data 6

(

ANI1)

Data 8

(ANI1)

Data 4

(ANI0)

Data 3

(ANI0)

ADCE is cleared to 0.

<10>

The trigger is not

acknowledged.

Trigger

standby

status

ADCS is set to 1.

<2>

ADCS retains

the value 1.

<5>

<5>

<5>

A hardware trigger

is generated.

<3>

<3>

<3>

<3>

<3>

Conversion

standby

Conversion

standby

Conversion

standby

Conversion

standby

Conversion

standby

Conversion is

interrupted

and restarts.

Conversion is

interrupted

and restarts.

<4>

A hardware trigger is

generated during A/D

conversion operation.

<6>

<7>

<4>

<4>

ANI1

ADS is rewritten during

A/D conversion operation

(from ANI0 to ANI1).

<8>

<5>

ADCS is overwritten with 1 during

A/D conversion

operation.

<4>

Conversion is

interrupted

and restarts.

Conversion is

interrupted.

<9>

ADCS is cleared

to 0 during A/D

conversion

operation.

A/D conversion

ends.

The trigger is not

acknowledged.