RL78/G1A CHAPTER 3 CPU ARCHITECTURE

R01UH0305EJ0200 Rev.2.00 73

Jul 04, 2013

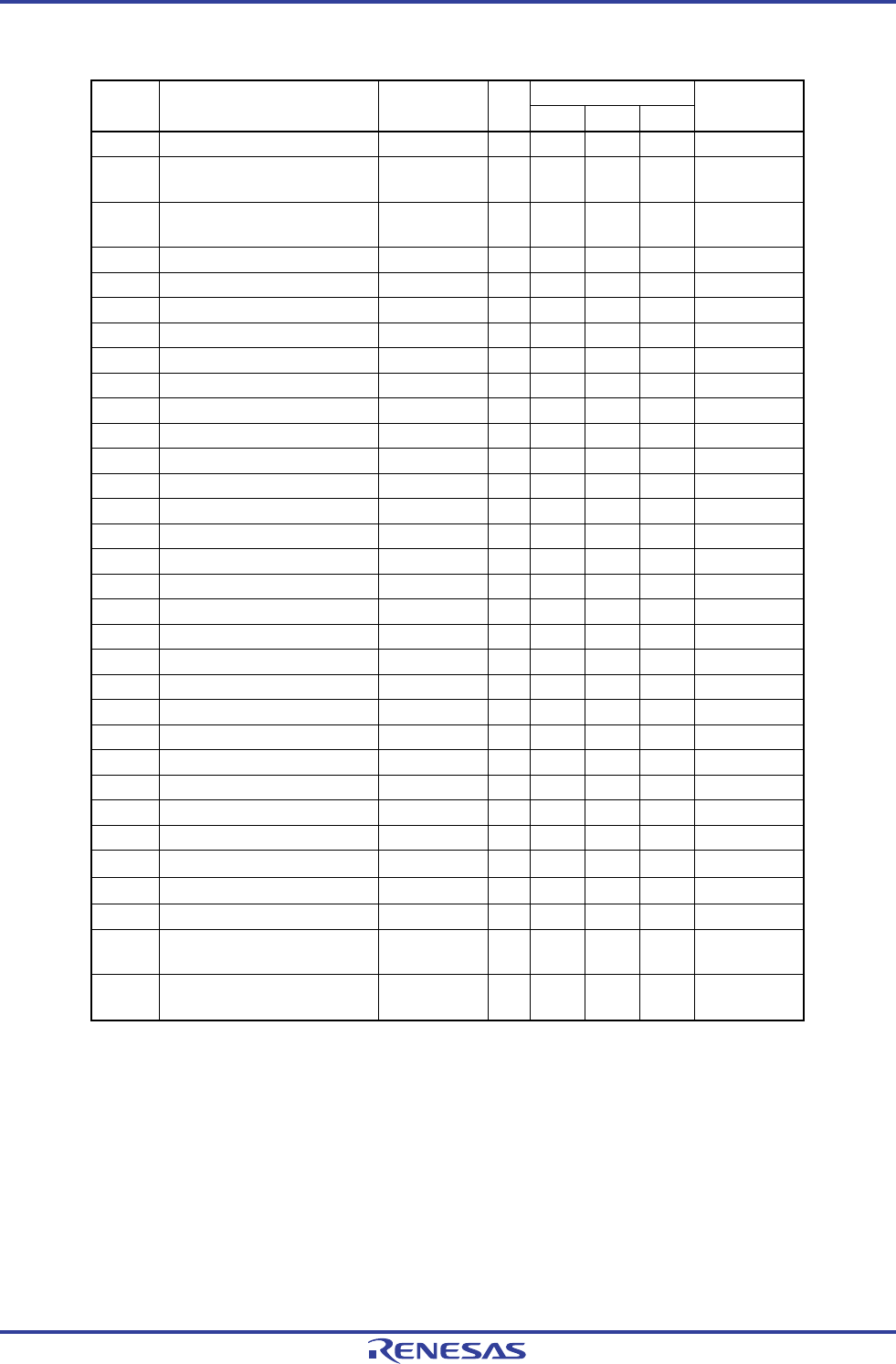

Table 3-6. Extended SFR (2nd SFR) List (1/6)

Manipulable Bit Range Address

Special Function Register (SFR) Name

Symbol R/W

1-bit 8-bit 16-bit

After Reset

F0010H A/D converter mode register 2 ADM2 R/W

√ √ −

00H

F0011H Conversion result comparison

upper limit setting register

ADUL R/W

− √ −

FFH

F0012H Conversion result comparison

lower limit setting register

ADLL R/W

− √ −

00H

F0013H A/D test register ADTES R/W

− √ −

00H

F0030H Pull-up resistor option register 0 PU0 R/W

√ √ −

00H

F0031H Pull-up resistor option register 1 PU1 R/W

√ √ −

00H

F0033H Pull-up resistor option register 3 PU3 R/W

√ √ −

00H

F0034H Pull-up resistor option register 4 PU4 R/W

√ √ −

01H

F0035H Pull-up resistor option register 5 PU5 R/W

√ √ −

00H

F0037H Pull-up resistor option register 7 PU7 R/W

√ √ −

00H

F003CH Pull-up resistor option register 12 PU12 R/W

√ √ −

00H

F003EH Pull-up resistor option register 14 PU14 R/W

√ √ −

00H

F0040H Port input mode register 0 PIM0 R/W

√ √ −

00H

F0041H Port input mode register 1 PIM1 R/W

√ √ −

00H

F0050H Port output mode register 0 POM0 R/W

√ √ −

00H

F0051H Port output mode register 1 POM1 R/W

√ √ −

00H

F0055H Port output mode register 5 POM5 R/W

√ √ −

00H

F0057H Port output mode register 7 POM7 R/W

√ √ −

00H

F0060H Port mode control register 0 PMC0 R/W

√ √ −

FFH

F0061H Port mode control register 1 PMC1 R/W

√ √ −

FFH

F0063H Port mode control register 3 PMC3 R/W

√ √ −

FFH

F0064H Port mode control register 4 PMC4 R/W

√ √ −

FFH

F0065H Port mode control register 5 PMC5 R/W

√ √ −

FFH

F0067H Port mode control register 7 PMC7 R/W

√ √ −

FFH

F006CH Port mode control register 12 PMC12 R/W

√ √ −

FFH

F0070H Noise filter enable register 0 NFEN0 R/W

√ √ −

00H

F0071H Noise filter enable register 1 NFEN1 R/W

√ √ −

00H

F0073H Input switch control register ISC R/W

√ √ −

00H

F0074H Timer input select register 0 TIS0 R/W

− √ −

00H

F0076H A/D port configuration register ADPC R/W

− √ −

00H

F0077H Peripheral I/O redirection

register

PIOR R/W

− √ −

00H

F0078H Invalid memory access

detection control register

IAWCTL R/W

− √ −

00H