RL78/G1A CHAPTER 18 STANDBY FUNCTION

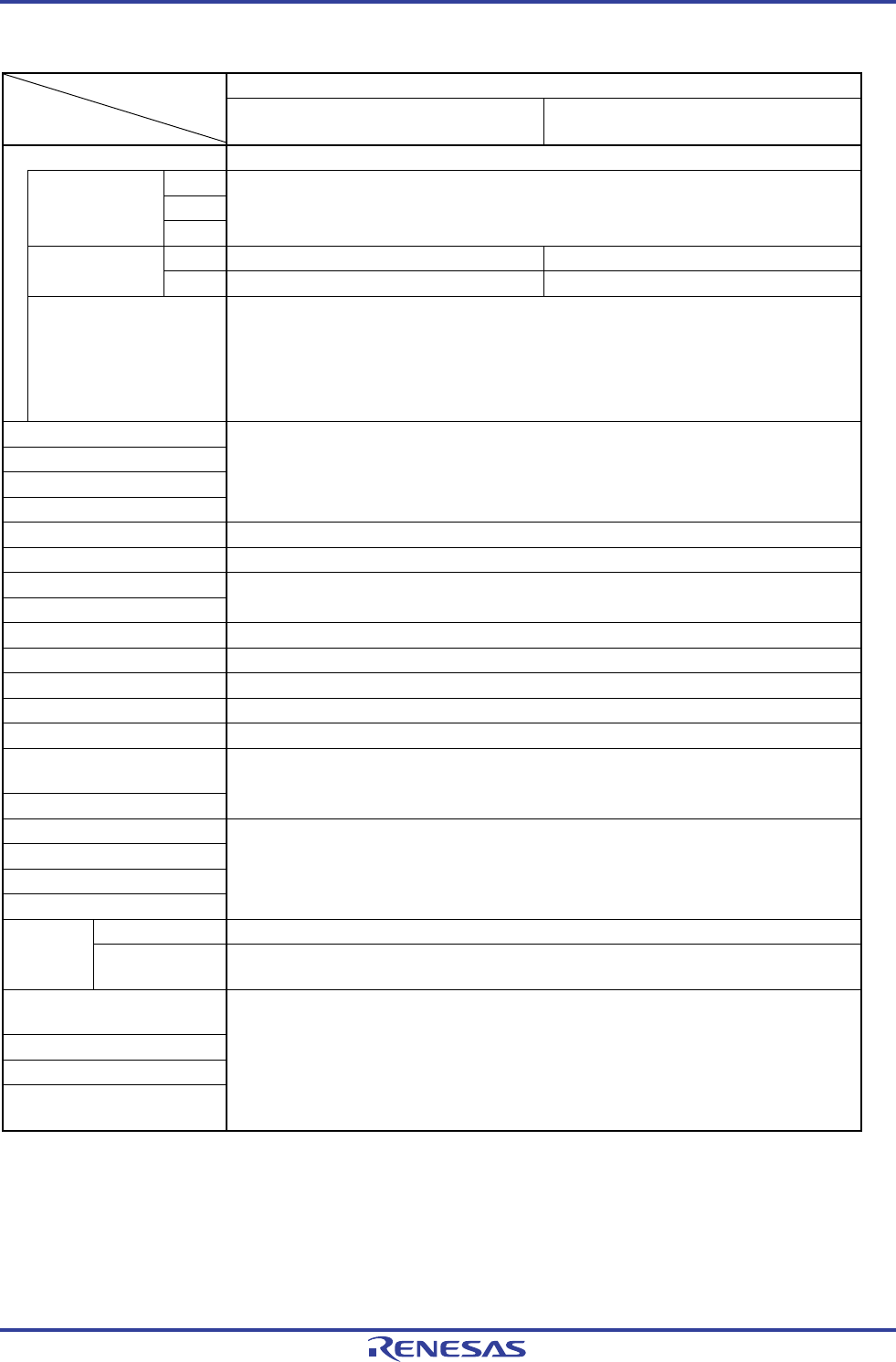

Table 18-1. Operating Statuses in HALT Mode (2/2)

Jul 04, 2013

Remark Operation stopped: Operation is automatically stopped before switching to the HALT mode.

Operation disabled: Operation is stopped before switching to the HALT mode.

fIH: High-speed on-chip oscillator clock fEX: External main system clock

f

IL: Low-speed on-chip oscillator clock fXT: XT1 clock

f

X: X1 clock fEXS: External subsystem clock

When HALT Instruction Is Executed While CPU Is Operating on Subsystem Clock HALT Mode Setting

Item

When CPU Is Operating on XT1 Clock (fXT) When CPU Is Operating on External

Subsystem Clock (f

EXS)

System clock Clock supply to the CPU is stopped

fIH

fX

Main system clock

fEX

Operation disabled

fXT Operation continues (cannot be stopped) Cannot operate

Subsystem clock

fEXS Cannot operate Operation continues (cannot be stopped)

fIL Set by bits 0 (WDSTBYON) and 4 (WDTON) of option byte (000C0H), and WUTMMCK0 bit of

subsystem clock supply mode control register (OSMC)

• WUTMMCK0 = 1: Oscillates

• WUTMMCK0 = 0 and WDTON = 0: Stops

• WUTMMCK0 = 0, WDTON = 1, and WDSTBYON = 1: Oscillates

• WUTMMCK0 = 0, WDTON = 1, and WDSTBYON = 0: Stops

CPU

Code flash memory

Data flash memory

RAM

Operation stopped

Port (latch) Status before HALT mode was set is retained

Timer array unit Operates when the RTCLPC bit is 0 (operation is disabled when the RTCLPC bit is not 0).

Real-time clock (RTC)

12-bit interval timer

Operable

Watchdog timer See CHAPTER 10 WATCHDOG TIMER

Clock output/buzzer output Operates when the RTCLPC bit is 0 (operation is disabled when the RTCLPC bit is not 0)

A/D converter Operation disabled

Serial array unit (SAU) Operates when the RTCLPC bit is 0 (operation is disabled when the RTCLPC bit is not 0).

Serial interface (IICA) Operation disabled

Multiplier and divider/multiply-

accumulator

DMA controller

Operates when the RTCLPC bit is 0 (operation is disabled when the RTCLPC bit is not 0).

Power-on-reset function

Voltage detection function

External interrupt

Key interrupt function

Operable

High-speed CRC Operation disabled CRC

operation

function

General-purpose

CRC

Operation stopped

RAM parity error detection

function

RAM guard function

SFR guard function

Illegal-memory access detection

function

Operation stopped

R01UH0305EJ0200 Rev.2.00 729