RL78/G1A CHAPTER 11 A/D CONVERTER

R01UH0305EJ0200 Rev.2.00 350

Jul 04, 2013

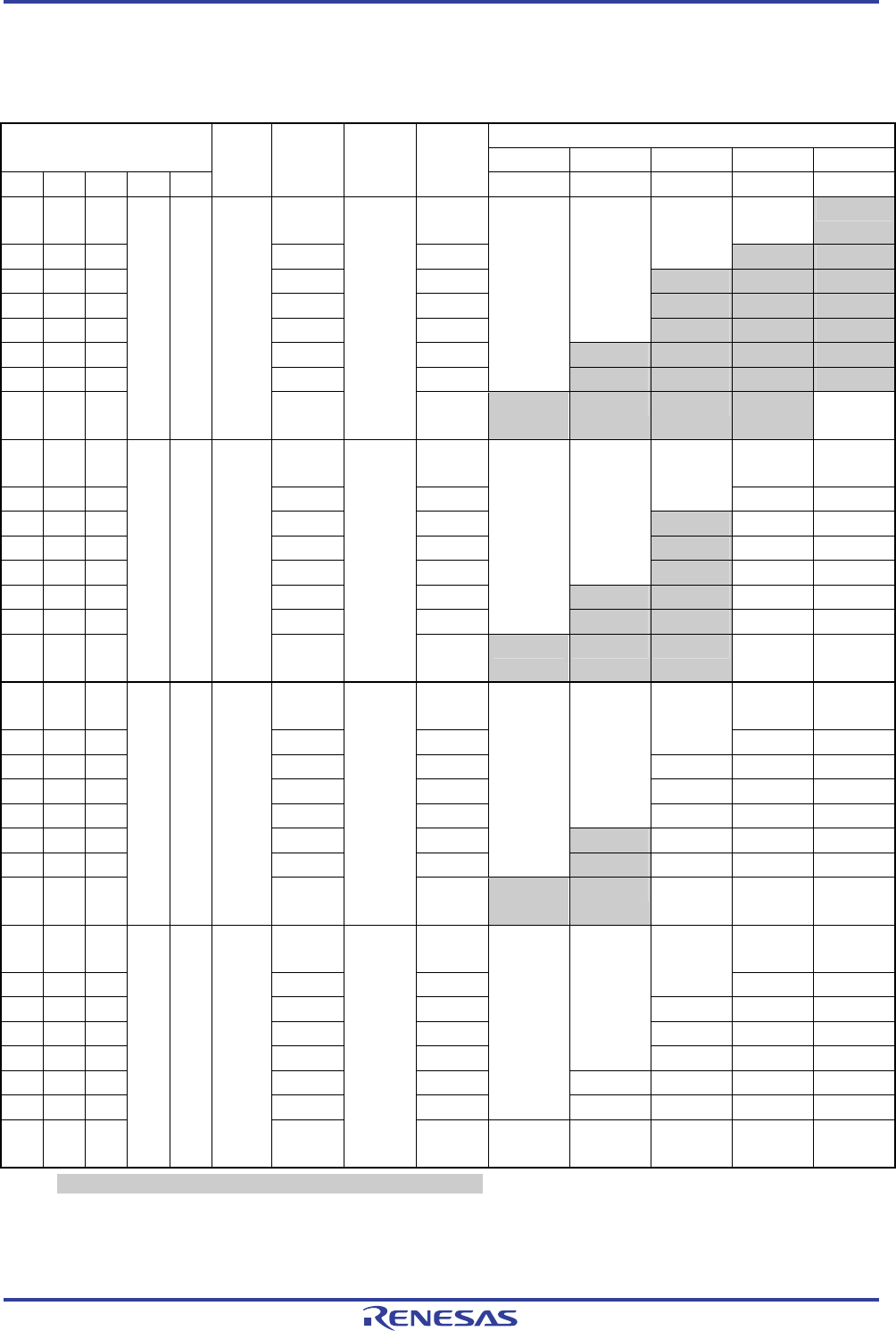

Table 11-3. A/D Conversion Time Selection (1/4)

(1) 12-bit resolution mode (ADTYP = 0) When there is no stabilization wait time

(software trigger mode/hardware trigger no-wait mode)

Conversion Time Selection

A/D Converter Mode Register 0

(ADM0)

AV

DD

= 1.6 to 3.6 V AV

DD

= 1.6 to 3.6 V AV

DD

= 1.8 to 3.6 V AV

DD

= 2.4 to 3.6 V AV

DD

= 2.7 to 3.6 V

FR2 FR1 FR0 LV1 LV0

Mode Conversion

Clock (f

AD)

Number of

Conversion

Clock

Conversion

Time

f

CLK = 1 MHz fCLK = 4 MHz fCLK = 8 MHz fCLK = 16 MHz fCLK = 32 MHz

0 0 0 fCLK/32 1728/fCLK Setting

prohibited

54

μ

s

Note

0 0 1 fCLK/16 864/fCLK

Setting

prohibited

54

μ

s

Note

27

μ

s

Note

0 1 0 fCLK/8 432/fCLK 54

μ

s

Note

27

μ

s

Note

13.5

μ

s

Note

0 1 1 fCLK/6 324/fCLK 40.5

μ

s

Note

20.25

μ

s

Note

10.125

μ

s

Note

1 0 0 fCLK/5 270/fCLK

Setting

prohibited

33.75

μ

s

Note

16.875

μ

s

Note

8.4375

μ

s

Note

1 0 1 fCLK/4 216/fCLK 54

μ

s

Note

27

μ

s

Note

13.5

μ

s

Note

6.75

μ

s

Note

1 1 0 fCLK/2 108/fCLK

Setting

prohibited

27

μ

s

Note

13.5

μ

s

Note

6.75

μ

s

Note

3.375

μ

s

Note

1 1 1

0 0 Normal 1

fCLK/1

54 f

AD

(number

of

sampling

clock:

11 f

AD)

54/f

CLK 54

μ

s

Note

13.5

μ

s

Note

6.75

μ

s

Note

3.375

μ

s

Note

Setting

prohibited

0 0 0 fCLK/32 2112/fCLK Setting

prohibited

66

μ

s

0 0 1 fCLK/16 1056/fCLK

Setting

prohibited

66

μ

s 33

μ

s

0 1 0 fCLK/8 528/fCLK 66

μ

s

Note

33

μ

s 16.5

μ

s

0 1 1 fCLK/6 396/fCLK 49.5

μ

s

Note

24.75

μ

s 12.375

μ

s

1 0 0 fCLK/5 330/fCLK

Setting

prohibited

41.25

μ

s

Note

20.625

μ

s 10.3125

μ

s

1 0 1 fCLK/4 264/fCLK 66

μ

s

Note

33

μ

s

Note

16.5

μ

s 8.25

μ

s

1 1 0 fCLK/2 132/fCLK

Setting

prohibited

33

μ

s

Note

16.5

μ

s

Note

8.25

μ

s 4.125

μ

s

1 1 1

0 1 Normal 2

fCLK/1

66 f

AD

(number

of

sampling

clock:

23 f

AD)

66/f

CLK 66

μ

s

Note

16.5

μ

s

Note

8.25

μ

s

Note

4.125

μ

s Setting

prohibited

0 0 0 fCLK/32 2432/fCLK Setting

prohibited

76

μ

s

0 0 1 fCLK/16 1216/fCLK

Setting

prohibited

76

μ

s 38

μ

s

0 1 0 fCLK/8 608/fCLK 76

μ

s 38

μ

s 19

μ

s

0 1 1 fCLK/6 456/fCLK 57

μ

s 28.5

μ

s 14.25

μ

s

1 0 0 fCLK/5 380/fCLK

Setting

prohibited

47.5

μ

s 23.75

μ

s 11.875

μ

s

1 0 1 fCLK/4 304/fCLK 76

μ

s

Note

38

μ

s 19

μ

s 9.5

μ

s

1 1 0 fCLK/2 152/fCLK

Setting

prohibited

38

μ

s

Note

19

μ

s 9.5

μ

s 4.75

μ

s

1 1 1

1 0 Low-

voltage 1

fCLK/1

76 f

AD

(number

of

sampling

clock:

33 f

AD)

76/f

CLK 76

μ

s

Note

19

μ

s

Note

9.5

μ

s 4.75

μ

s Setting

prohibited

0 0 0 fCLK/32 7360/fCLK Setting

prohibited

230

μ

s

0 0 1 fCLK/16 3680/fCLK

Setting

prohibited

230

μ

s 115

μ

s

0 1 0 fCLK/8 1840/fCLK 230

μ

s 115

μ

s 57.5

μ

s

0 1 1 fCLK/6 1380/fCLK 172.5

μ

s 86.25

μ

s 43.125

μ

s

1 0 0 fCLK/5 1150/fCLK

Setting

prohibited

143.75

μ

s 71.875

μ

s 35.9375

μ

s

1 0 1 fCLK/4 920/fCLK 230

μ

s 115

μ

s 57.5

μ

s 28.75

μ

s

1 1 0 fCLK/2 460/fCLK

Setting

prohibited

115

μ

s 57.5

μ

s 28.75

μ

s 14.375

μ

s

1 1 1

1 1 Low-

voltage 2

fCLK/1

230 f

AD

(number

of

sampling

clock:

187 f

AD)

230/f

CLK 230

μ

s 57.5

μ

s 28.75

μ

s 14.375

μ

s Setting

prohibited

Note When using ANI16 to ANI30, setting this value is prohibited.

(Cautions and Remark are listed on the next page.)

<R>