RL78/G1A CHAPTER 13 SERIAL INTERFACE IICA

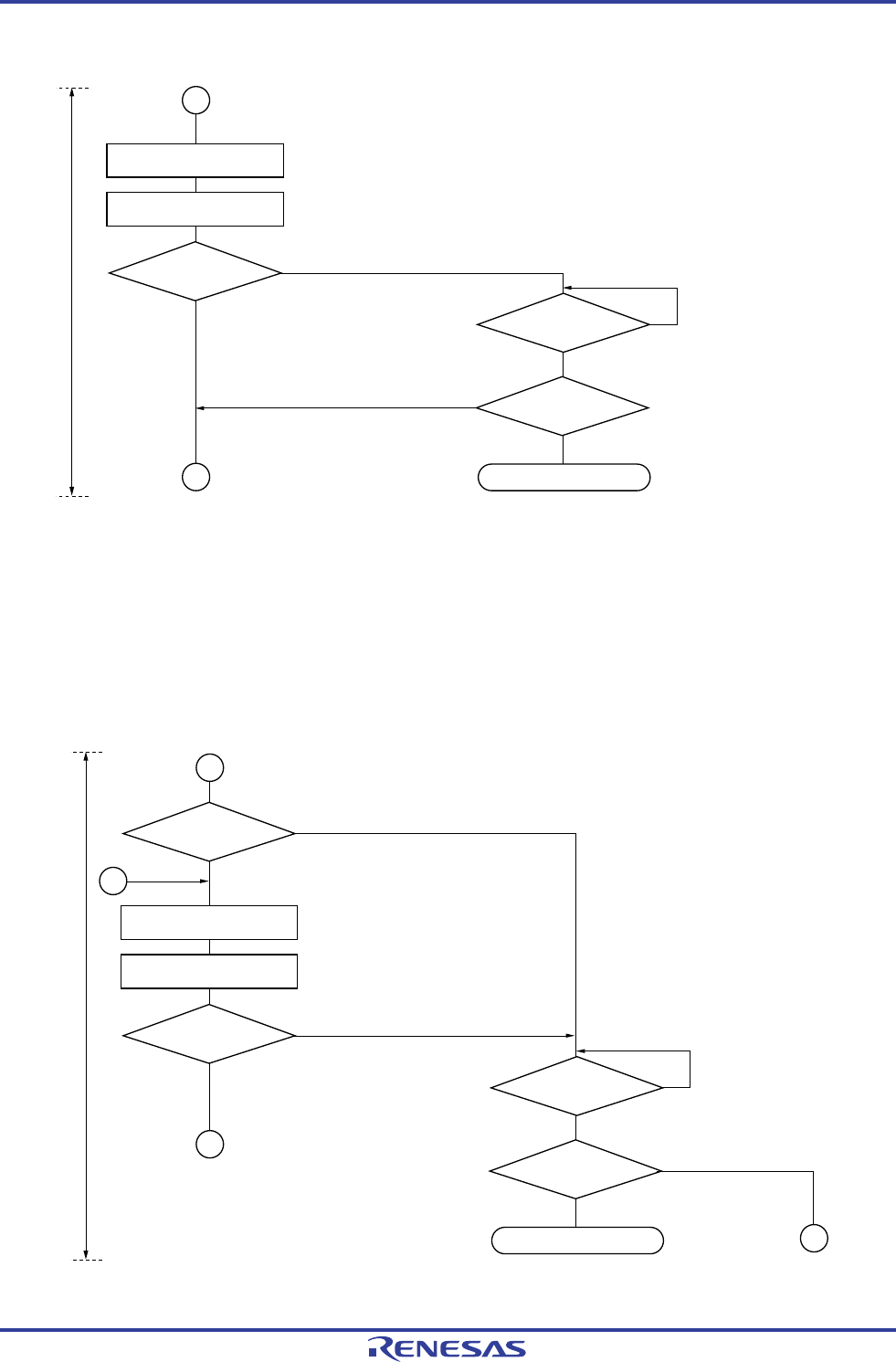

Figure 13-29. Master Operation in Multi-Master System (2/4)

No

STT0 = 1

Wait

Slave operation

Yes

MSTS0 = 1?

EXC0 = 1 or COI0 =1?

Prepares for starting communication

(generates a start condition).

Secure wait time

Note

by software.

Waits for bus release

(communication being reserved).

Wait state after stop condition

was detected and start condition

was generated by the communication

reservation function.

No

INTIICA0

interrupt occurs?

Yes

Yes

No

A

C

Enables reserving communication.

Communication processing

Note The wait time (number of clocks of fMCK) is calculated as follows.

<R>

(IICWL0 setting value + IICWH0 setting value + 4) + t

F × 2 × fMCK [clocks]

Remark IICWL0: IICA low-level width setting register 0

IICWH0: IICA high-level width setting register 0

t

F: SDAA0 and SCLA0 signal falling times

f

MCK: IICA operation clock frequency

Figure 13-29. Master Operation in Multi-Master System (3/4)

Yes

No

No

Yes

Yes

No

Yes

No

B

D

C

D

STT0 = 1

Wait

Note

Slave operation

IICBSY0 = 0?

EXC0 = 1 or COI0 =1?

Prepares for starting communication

(generates a start condition).

Disables reserving communication.

Waits for bus release

Detects a stop condition.

INTIICA0

interrupt occurs?

STCF0 = 0?

Communication processing

Note Wait: Wait for five clocks of f

MCL

<R>

R01UH0305EJ0200 Rev.2.00 612

Jul 04, 2013