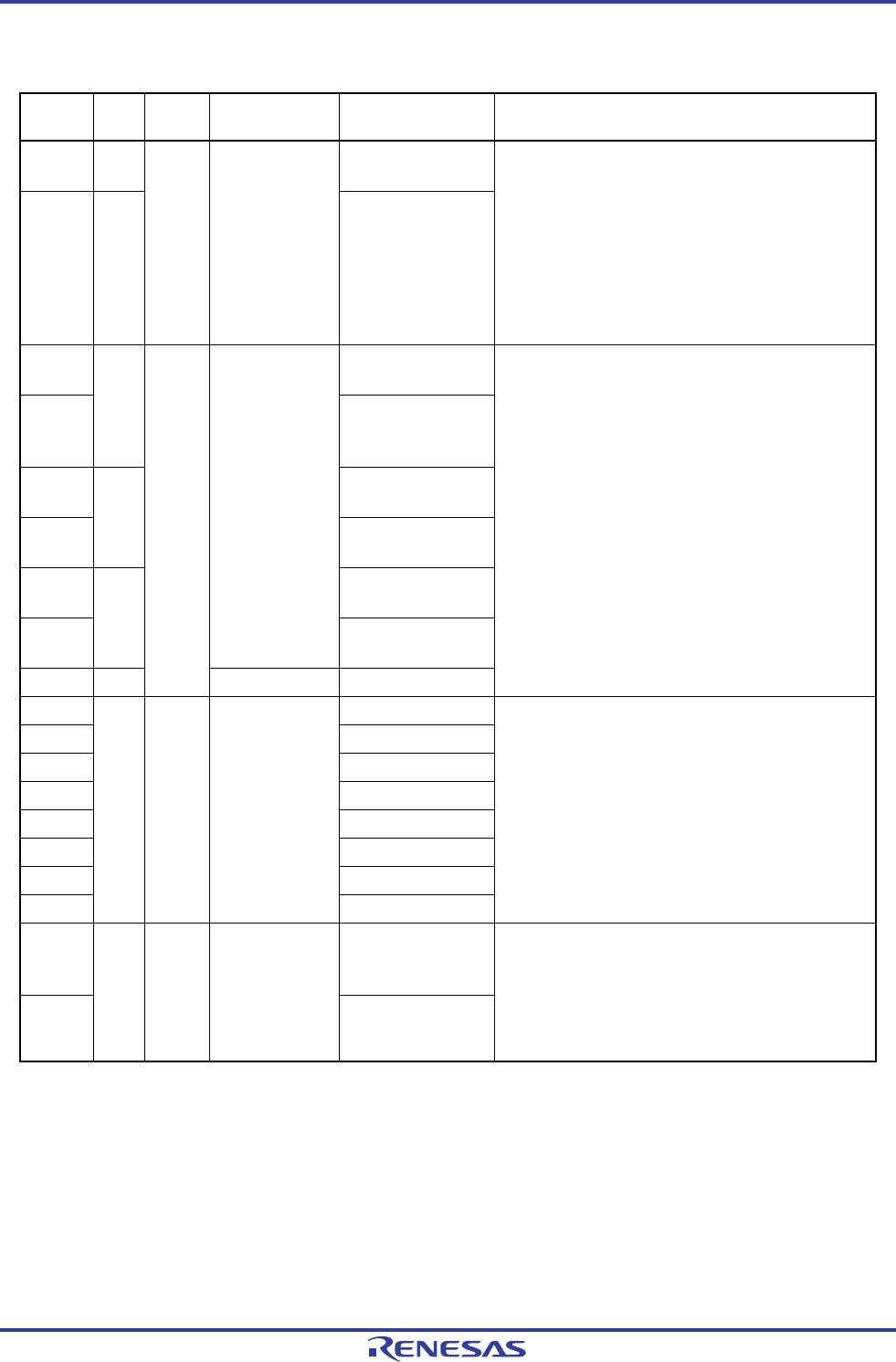

RL78/G1A CHAPTER 2 PIN FUNCTIONS

2.1.3 48-pin products

(1/2)

Function

Name

Pin

Type

I/O After Reset Alternate Function Function

P02 7-3-2

ANI17/TI00/TxD1/

(KR0)

P03 8-3-2

I/O Analog input port

ANI16TO00/RxD1/

(KR1)

Port 0.

2-bit I/O port.

Input/output can be specified in 1-bit units.

Use of an on-chip pull-up resistor can be specified by a

software setting at input port.

Input of P03 can be set to TTL input buffer.

Output of P02 and P03 can be set to N-ch open-drain

output (V

DD tolerance).

Can be set to analog input

Note 1

.

P10

ANI18/SCK00/

SCL00/(KR0)

P11

8-3-2

ANI20/SI00/RxD0/

TOOLRxD/SDA00/

(KR1)

P12

ANI21/SO00/TxD0/

TOOLTxD/(KR2)

P13

7-3-2

ANI22/TxD2/SO20/

(KR3)

P14

ANI23/RxD2/SI20/

SDA20/(KR4)

P15

8-3-2

Analog input port

ANI24/PCLBUZ1/

SCK20/SCL20/(KR5)

P16 8-1-1

I/O

Input port

TI01/TO01/INTP5

Port 1.

7-bit I/O port.

Input/output can be specified in 1-bit units.

Use of an on-chip pull-up resistor can be specified by a

software setting at input port.

Input of P10, P11, and P14 to P16 can be set to TTL

input buffer.

Output of P10 to P15 can be set to N-ch open-drain

output (V

DD tolerance).

P10 to P15 can be set to analog input

Note 1

.

P20

ANI0/AV

REFP

P21

ANI1/AV

REFM

P22

ANI2/(KR2)

P23

ANI3/(KR3)

P24

ANI4/(KR4)

P25

ANI5/(KR5)

P26

ANI6

P27

4-3-1 I/O Analog input port

ANI7

Port 2.

8-bit I/O port.

Input/output can be specified in 1-bit units.

Can be set to analog input

Note 2

.

P30

ANI27/INTP3/

RTC1HZ/SCK11/

SCL11

P31

7-3-1 I/O Analog input port

ANI29/TI03/TO03/

INTP4

Port 3.

2-bit I/O port.

Input/output can be specified in 1-bit units.

Use of an on-chip pull-up resistor can be specified by a

software setting at input port.

Can be set to analog input

Note 1

.

<R>

Notes 1. Digital or analog for each pin can be selected with the port mode control register x (PMCx) (can be set in 1-

bit units).

2. Digital or analog for each pin can be selected with the A/D port configuration register (ADPC).

Remark Functions in parentheses in the above figure can be assigned via settings in the peripheral I/O redirection

register (PIOR). See Figure 4-8 Format of Peripheral I/O Redirection Register (PIOR).

R01UH0305EJ0200 Rev.2.00 24

Jul 04, 2013