RL78/G1A CHAPTER 6 TIMER ARRAY UNIT

R01UH0305EJ0200 Rev.2.00 264

Jul 04, 2013

6.8.6 Operation as delay counter

It is possible to start counting down when the valid edge of the TImn pin input is detected (an external event), and then

generate INTTMmn (a timer interrupt) after any specified interval.

It is also possible to start counting down and generate INTTMmn (timer interrupt) at any interval by setting TSmn to 1

by software while TEmn = 1.

The interrupt generation period can be calculated by the following expression.

Generation period of INTTMmn (timer interrupt) = Period of count clock × (Set value of TDRmn + 1)

Timer count register mn (TCRmn) operates as a down counter in the one-count mode.

When the channel start trigger bit (TSmn, TSHm1, TSHm3) of timer channel start register m (TSm) is set to 1, the

TEmn, TEHm1, TEHm3 bits are set to 1 and the TImn pin input valid edge detection wait status is set.

Timer count register mn (TCRmn) starts operating upon TImn pin input valid edge detection and loads the value of

timer data register mn (TDRmn). The TCRmn register counts down from the value of the TDRmn register it has loaded, in

synchronization with the count clock. When TCRmn = 0000H, it outputs INTTMmn and stops counting until the next TImn

pin input valid edge is detected.

The TDRmn register can be rewritten at any time. The new value of the TDRmn register becomes valid from the next

period.

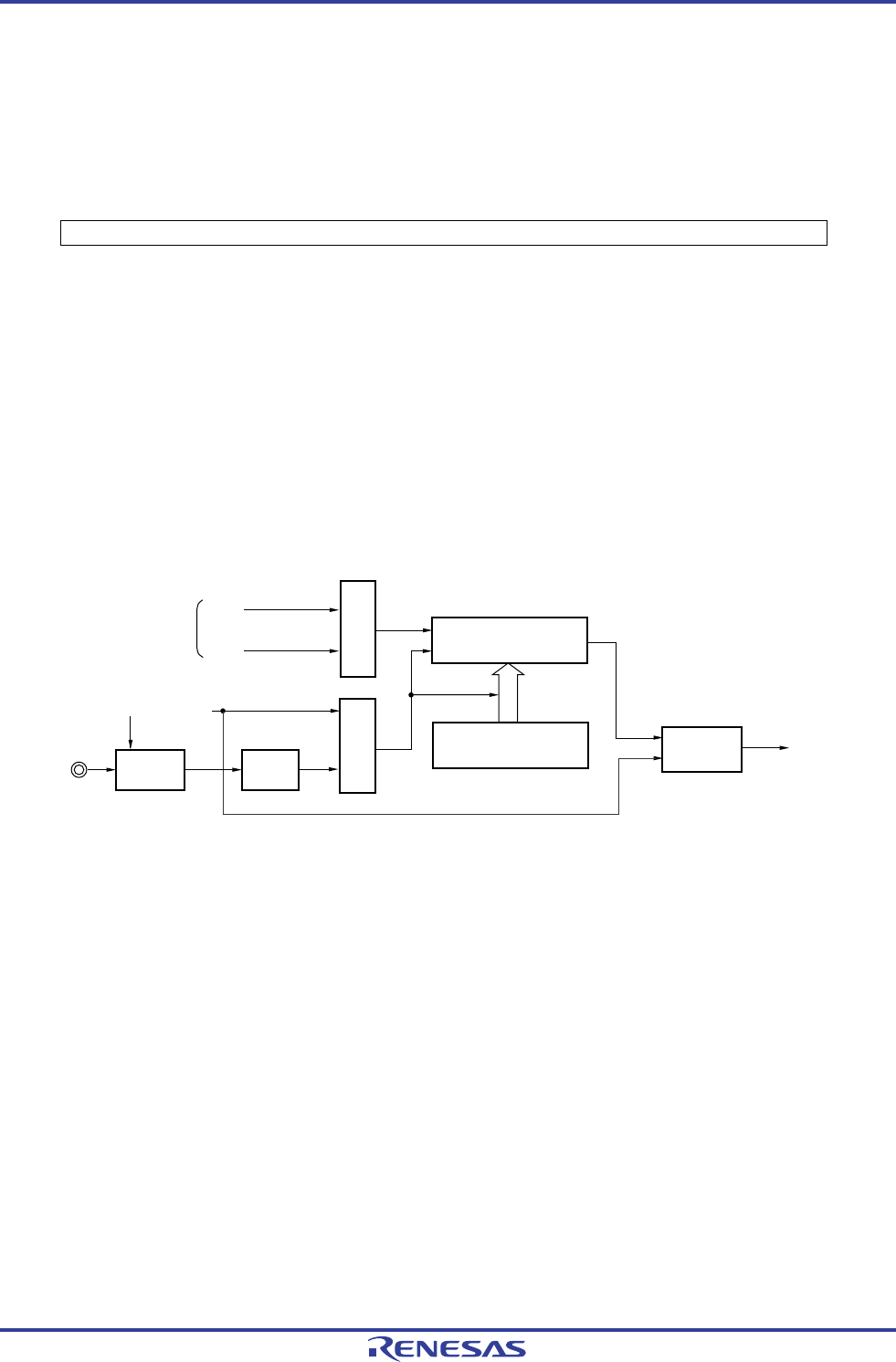

Figure 6-61. Block Diagram of Operation as Delay Counter

Interrupt signal

(INTTMmn)

Interrupt

controller

Operation clock

Note

CKm0

CKm1

TSmn

Clock selection

Trigger selection

Timer counter

register mn (TCRmn)

Timer data

register mn (TDRmn)

Edge

detection

TImn pin

Noise

filter

TNFENxx

Note For using channels 1 and 3, the clock can be selected from CKm0, CKm1, CKm2 and CKm3.

Remark m: Unit number (m = 0), n: Channel number (n = 0 to 7 (however, timer input pin (TImn), timer output pin

(TOmn) : n = 0, 1, 3 to 7))