RL78/G1A CHAPTER 13 SERIAL INTERFACE IICA

13.4 I

2

C Bus Mode Functions

13.4.1 Pin configuration

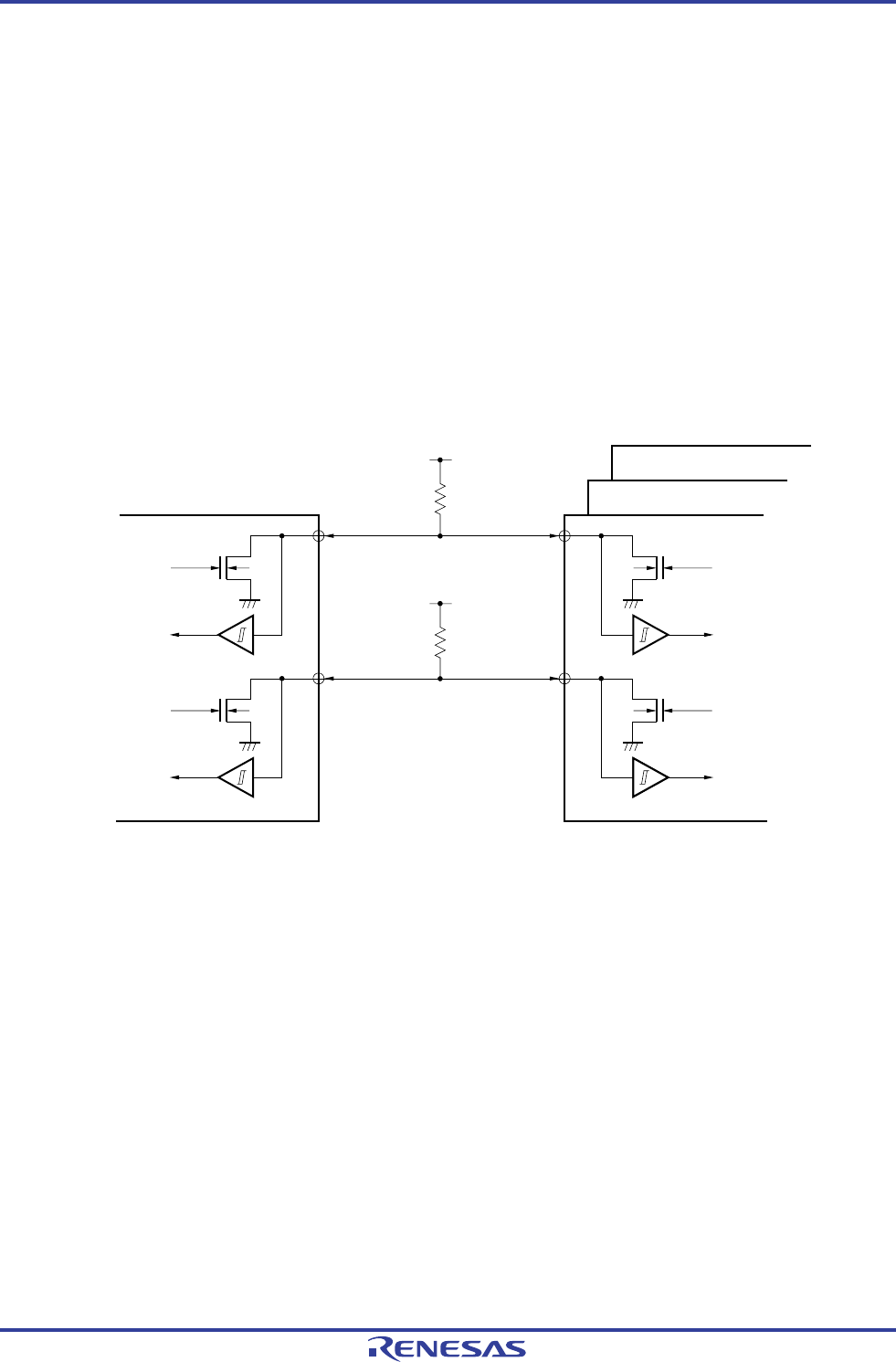

The serial clock pin (SCLA0) and the serial data bus pin (SDAA0) are configured as follows.

(1) SCLA0 ....This pin is used for serial clock input and output.

This pin is an N-ch open-drain output for both master and slave devices. Input is Schmitt input.

(2) SDAA0.... This pin is used for serial data input and output.

This pin is an N-ch open-drain output for both master and slave devices. Input is Schmitt input.

Since outputs from the serial clock line and the serial data bus line are N-ch open-drain outputs, an external pull-up

resistor is required.

Figure 13-13. Pin Configuration Diagram

Master device

Clock output

(Clock input)

Data output

Data input

V

SS

VSS

SCLA0

SDAA0

V

DD

VDD

(Clock output)

Clock input

Data output

Data input

V

SS

VSS

Slave device

SCLA0

SDAA0

R01UH0305EJ0200 Rev.2.00 587

Jul 04, 2013