RL78/G1A CHAPTER 21 VOLTAGE DETECTOR

When setting an interrupt and reset mode (LVIMDS1, LVIMDS0 = 1, 0), voltage detection stabilization wait time for 400

μ

s or 5 clocks of fIL is necessary after LVD reset is released (LVIRF = 1). After waiting until voltage detection stabilizes,

(0) clear the LVIMD bit for initialization. While voltage detection stabilization wait time is being counted and when the

LVIMD bit is rewritten, set LVISEN to 1 to mask a reset or interrupt generation by LVD.

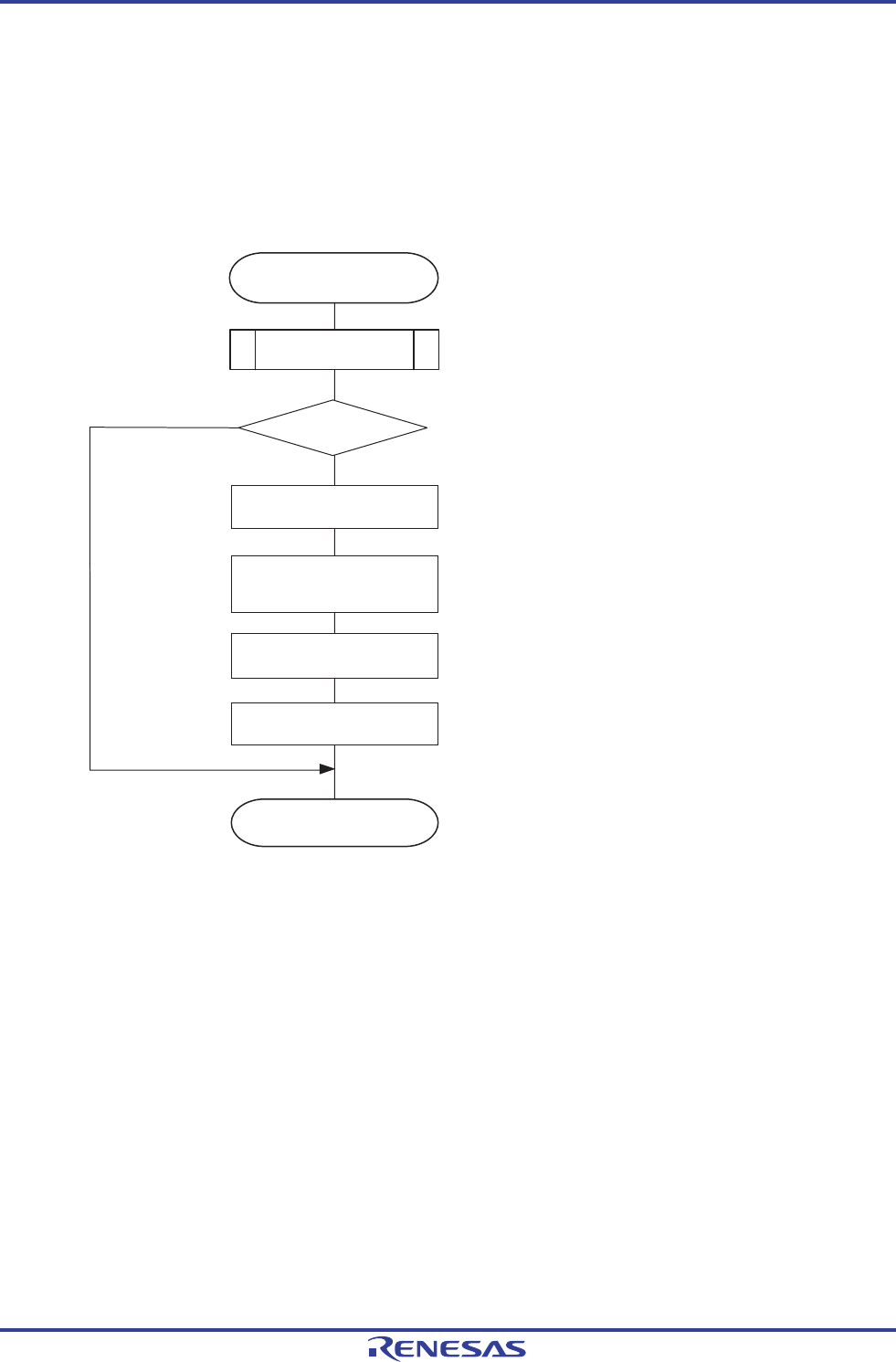

Figure 21-8 shows the procedure for initial setting of interrupt and reset mode.

Figure 21-8. Initial Setting of Interrupt and Reset Mode

<R>

Set the LVIMD bit to 0 to set interrupt mode.

LVISEN = 1

LVIMD = 0

Set the LVISEN bit to 1 to mask voltage detection

(LVIOMSK = 1)

Count 400

μ

s or 5 clocks of f

IL

by software.

LVISEN = 0

Set the LVISEN bit to 0 to enable voltage detection.

Yes

No

LVIRF = 1 ?

Check internal reset generation by LVD circuit

Voltage detection stabilization

wait time

Normal operation

Power application

Check reset source

See Figure 19-5 Procedure for Checking Reset Resource.

Remark fIL: Low-speed on-chip oscillator clock frequency

R01UH0305EJ0200 Rev.2.00 769

Jul 04, 2013