RL78/G1A CHAPTER 13 SERIAL INTERFACE IICA

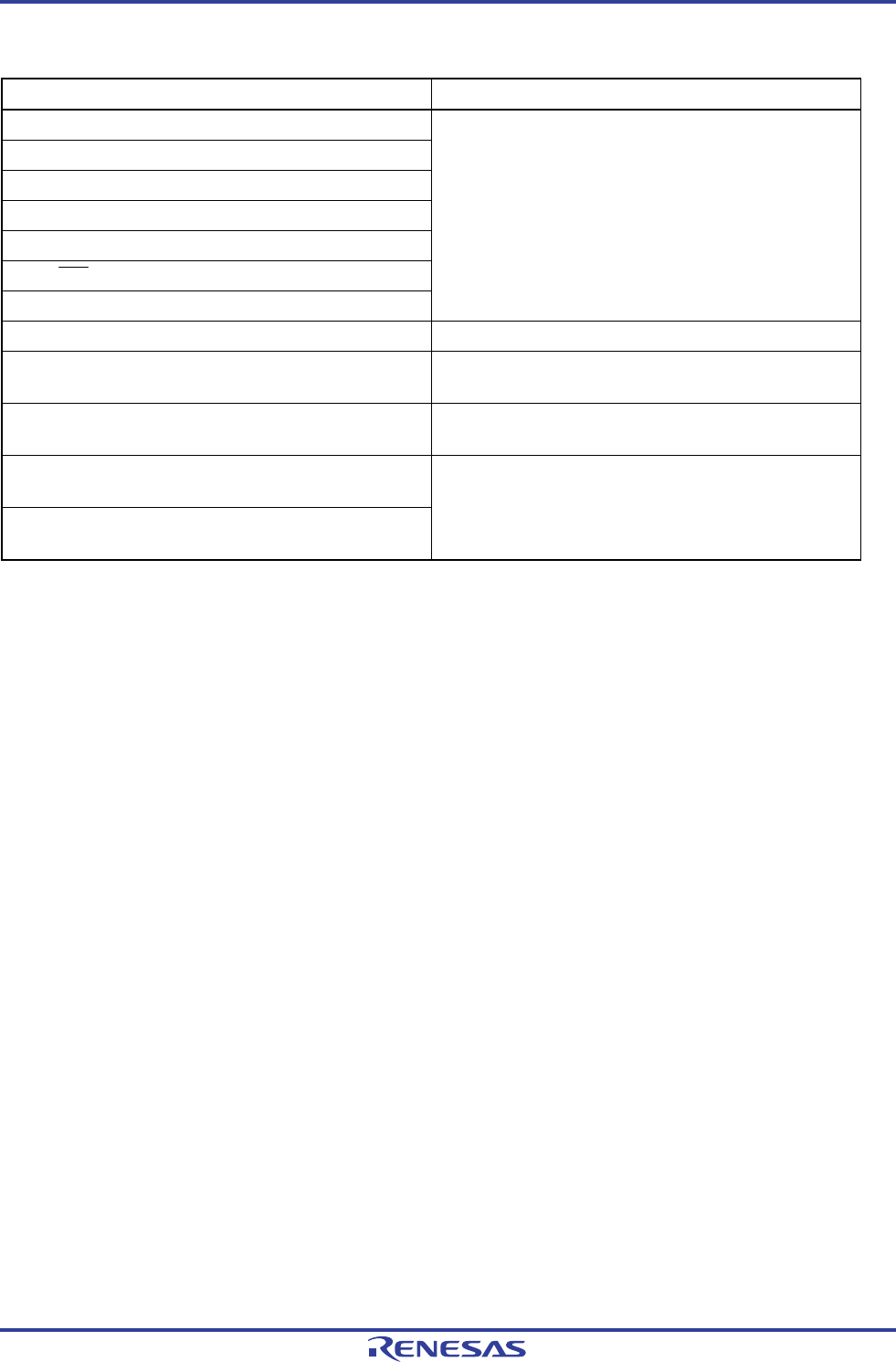

Table 13-4. Status During Arbitration and Interrupt Request Generation Timing

Status During Arbitration Interrupt Request Generation Timing

Jul 04, 2013

During address transmission At falling edge of eighth or ninth clock following byte transfer

Note 1

Read/write data after address transmission

During extension code transmission

Read/write data after extension code transmission

During data transmission

During ACK transfer period after data transmission

When restart condition is detected during data transfer

When stop condition is generated (when SPIE0 = 1)

Note 2

When stop condition is detected during data transfer

At falling edge of eighth or ninth clock following byte transfer

Note 1

When data is at low level while attempting to generate a restart

condition

When stop condition is generated (when SPIE0 = 1)

Note 2

When stop condition is detected while attempting to generate a

restart condition

When data is at low level while attempting to generate a stop

condition

At falling edge of eighth or ninth clock following byte transfer

Note 1

When SCLA0 is at low level while attempting to generate a

restart condition

Notes 1. When the WTIM0 bit (bit 3 of IICA control register 00 (IICCTL00)) = 1, an interrupt request occurs at the

falling edge of the ninth clock. When WTIM0 = 0 and the extension code’s slave address is received, an

interrupt request occurs at the falling edge of the eighth clock.

2. When there is a chance that arbitration will occur, set SPIE0 = 1 for master device operation.

Remark SPIE0: Bit 4 of IICA control register 00 (IICCTL00)

R01UH0305EJ0200 Rev.2.00 600