RL78/G1A CHAPTER 15 DMA CONTROLLER

15.4.2 Transfer mode

The following four modes can be selected for DMA transfer by using bits 6 and 5 (DRSn and DSn) of DMA mode

control register n (DMCn).

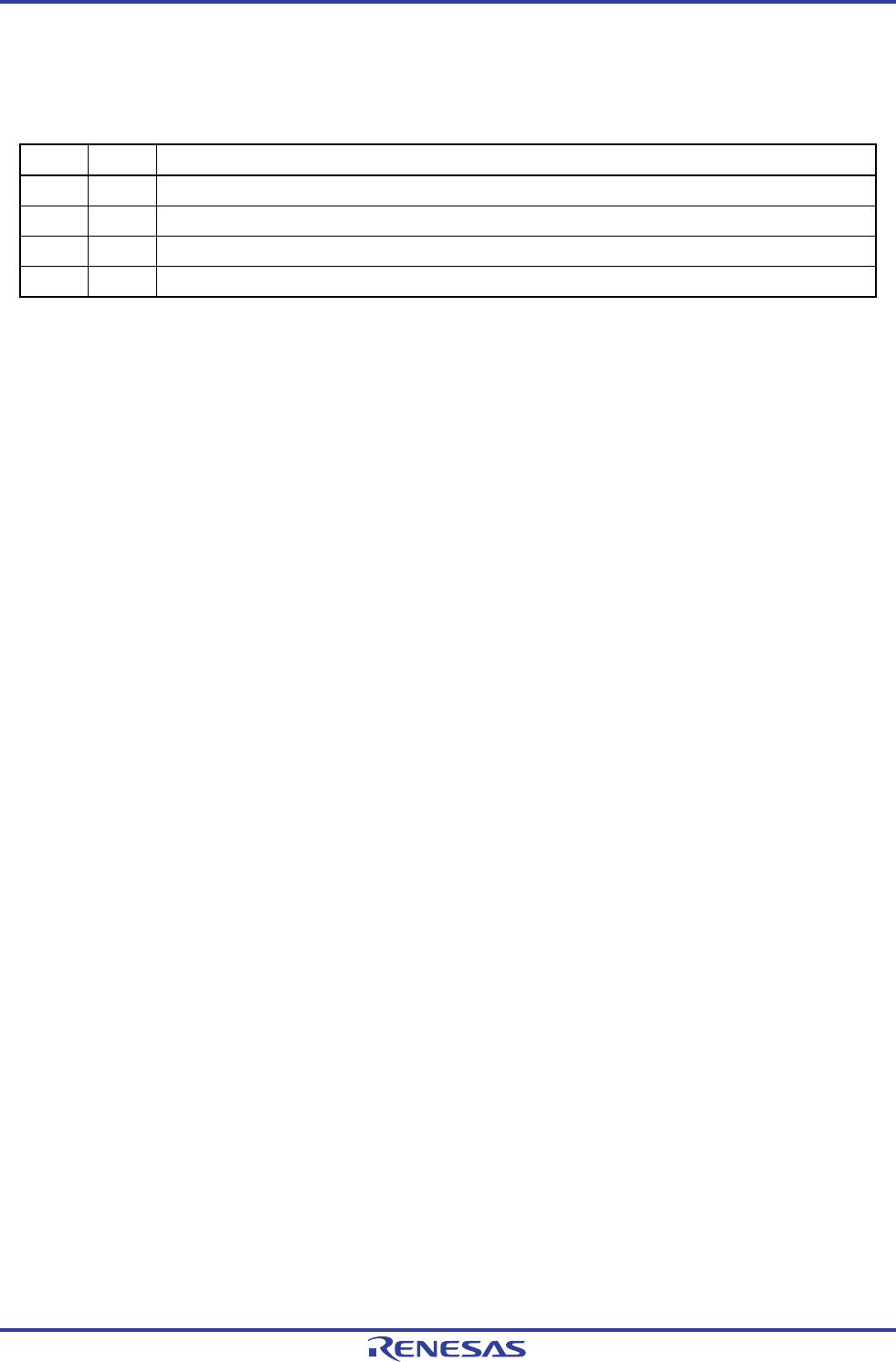

DRSn DSn DMA Transfer Mode

0 0 Transfer from SFR of 1-byte data (fixed address) to RAM (address is incremented by +1)

0 1 Transfer from SFR of 2-byte data (fixed address) to RAM (address is incremented by +2)

1 0 Transfer from RAM of 1-byte data (address is incremented by +1) to SFR (fixed address)

1 1 Transfer from RAM of 2-byte data (address is incremented by +2) to SFR (fixed address)

By using these transfer modes, up to 1024 bytes of data can be consecutively transferred by using the serial interface,

data resulting from A/D conversion can be consecutively transferred, and port data can be scanned at fixed time intervals

by using a timer.

15.4.3 Termination of DMA transfer

When DBCn = 00H and DMA transfer is completed, the DSTn bit is automatically cleared to 0. An interrupt request

(INTDMAn) is generated and transfer is terminated.

When the DSTn bit is cleared to 0 to forcibly terminate DMA transfer, DMA byte count register n (DBCn) and DMA RAM

address register n (DRAn) hold the value when transfer is terminated.

The interrupt request (INTDMAn) is not generated if transfer is forcibly terminated.

Remark n: DMA channel number (n = 0, 1)

R01UH0305EJ0200 Rev.2.00 676

Jul 04, 2013