RL78/G1A CHAPTER 28 INSTRUCTION SET

R01UH0305EJ0200 Rev.2.00 842

Jul 04, 2013

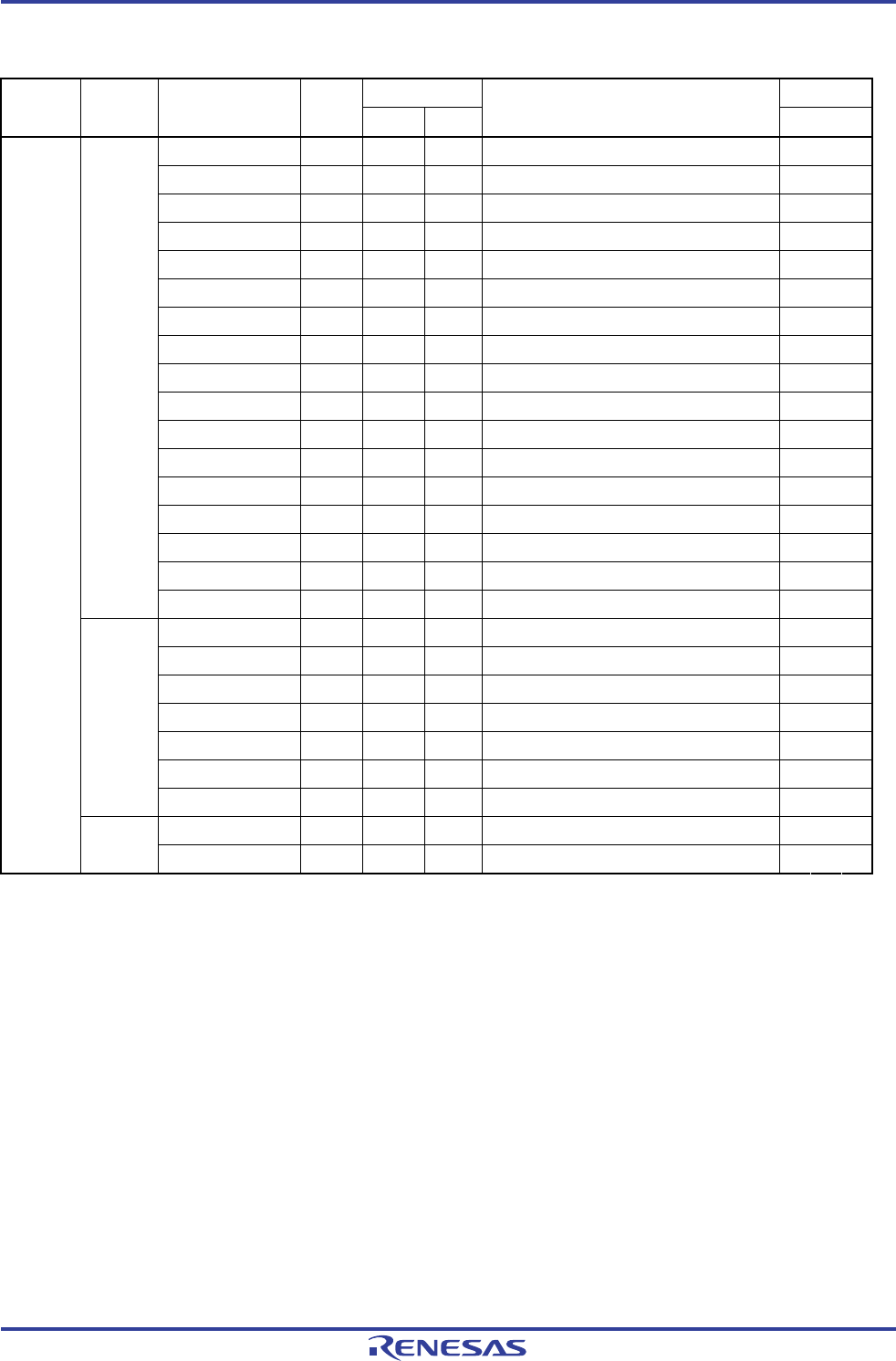

Table 28-5. Operation List (10/17)

Notes 1. Number of CPU clocks (f

CLK) when the internal RAM area, SFR area, or extended SFR area is accessed, or

when no data is accessed.

2. Number of CPU clocks (f

CLK) when the code flash memory is accessed, or when the data flash memory is

accessed by an 8-bit instruction.

3. Except r = A

Remark Number of clock is when program exists in the internal ROM (flash memory) area. If fetching the instruction

from the internal RAM area, the number becomes double number plus 3 clocks at a maximum.

Clocks Flag

Instruction

Group

Mnemonic Operands Bytes

Note 1 Note 2

Clocks

Z AC CY

A, #byte 2 1

−

A – byte × × ×

!addr16, #byte 4 1 4 (addr16) – byte × × ×

ES:!addr16, #byte 5 2 5 (ES:addr16) – byte × × ×

saddr, #byte 3 1

−

(saddr) – byte × × ×

A, r

Note3

2 1

−

A – r × × ×

r, A 2 1

−

r – A × × ×

A, !addr16 3 1 4 A – (addr16) × × ×

A, ES:!addr16 4 2 5 A – (ES:addr16) × × ×

A, saddr 2 1

−

A – (saddr) × × ×

A, [HL] 1 1 4 A – (HL) × × ×

A, ES:[HL] 2 2 5 A – (ES:HL) × × ×

A, [HL+byte] 2 1 4 A – (HL+byte) × × ×

A, ES:[HL+byte] 3 2 5 A – ((ES:HL)+byte) × × ×

A, [HL+B] 2 1 4 A – (HL+B) × × ×

A, ES:[HL+B] 3 2 5 A – ((ES:HL)+B) × × ×

A, [HL+C] 2 1 4 A – (HL+C) × × ×

CMP

A, ES:[HL+C] 3 2 5 A – ((ES:HL)+C) × × ×

A 1 1

−

A – 00H × 0 0

X 1 1

−

X – 00H × 0 0

B 1 1

−

B – 00H × 0 0

C 1 1

−

C – 00H × 0 0

!addr16 3 1 4 (addr16) – 00H × 0 0

ES:!addr16 4 2 5 (ES:addr16) – 00H × 0 0

CMP0

saddr 2 1

−

(saddr) – 00H × 0 0

X, [HL+byte] 3 1 4 X – (HL+byte) × × ×

8-bit

operation

CMPS

X, ES:[HL+byte] 4 2 5 X – ((ES:HL)+byte) × × ×

<R>