RL78/G1A CHAPTER 6 TIMER ARRAY UNIT

R01UH0305EJ0200 Rev.2.00 239

Jul 04, 2013

6.7 Timer Input (TImn) Control

6.7.1 TImn pin input circuit configuration

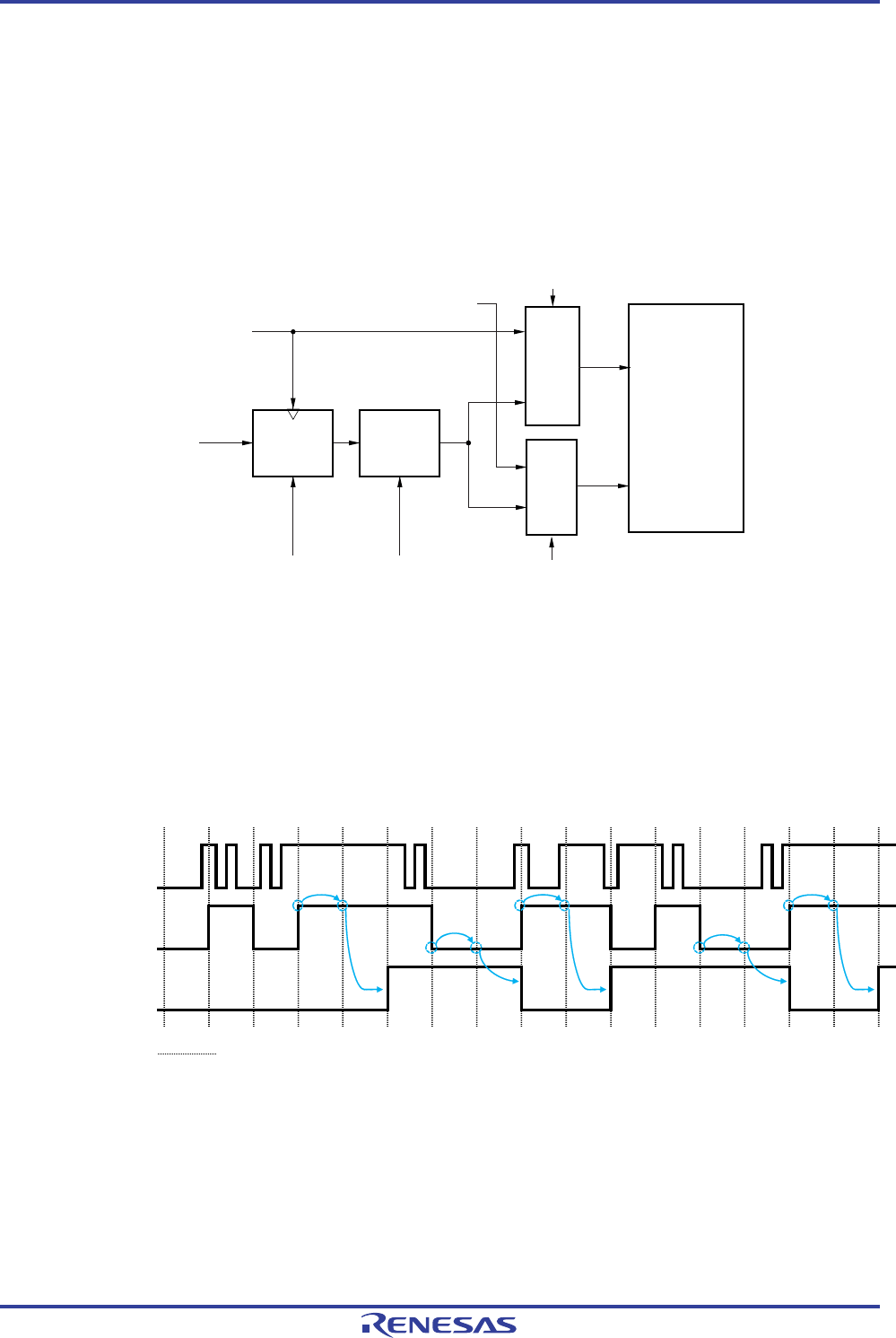

The signal input from a timer input pin passes through a noise filter and edge detector, and is then input to the timer

controller. If it is necessary to eliminate noise at the pin in question, enable its noise filter. The configuration of the input

circuit is shown below.

Figure 6-39. Iutput Circuit Configuration

Timer control

circuit

CCSmn

f

TCLK

f

MCK

TImn pin

TNFENmn CISmn1,

CISmn0

STSmn2 to

STSmn0

Noise

filter

Edge

detection

Interrupt signal from mater channel

Trigger

selection

Count clock

selection

6.7.2 Noise filter

If the noise filter is disabled, only synchronization is performed, based on the operating clock of channel n (fMCK). If the

noise filter is enabled, synchronization is performed based on the operating clock of channel n (f

MCK), and then two-clock

match detection is performed. The following shows the waveforms of a signal after passing through a noise filter when the

noise filter is enabled and disabled.

Figure 6-40.

Waveform of Sampling Signal Input to TImn Pin When Noise Filter Is Enabled and Disabled

TImn pin

Noise filter OFF

Noise filter ON

Operation clock(f

MCK

)