RL78/G1A CHAPTER 3 CPU ARCHITECTURE

R01UH0305EJ0200 Rev.2.00 62

Jul 04, 2013

3.2 Processor Registers

The RL78/G1A products incorporate the following processor registers.

3.2.1 Control registers

The control registers control the program sequence, statuses and stack memory. The control registers consist of a

program counter (PC), a program status word (PSW) and a stack pointer (SP).

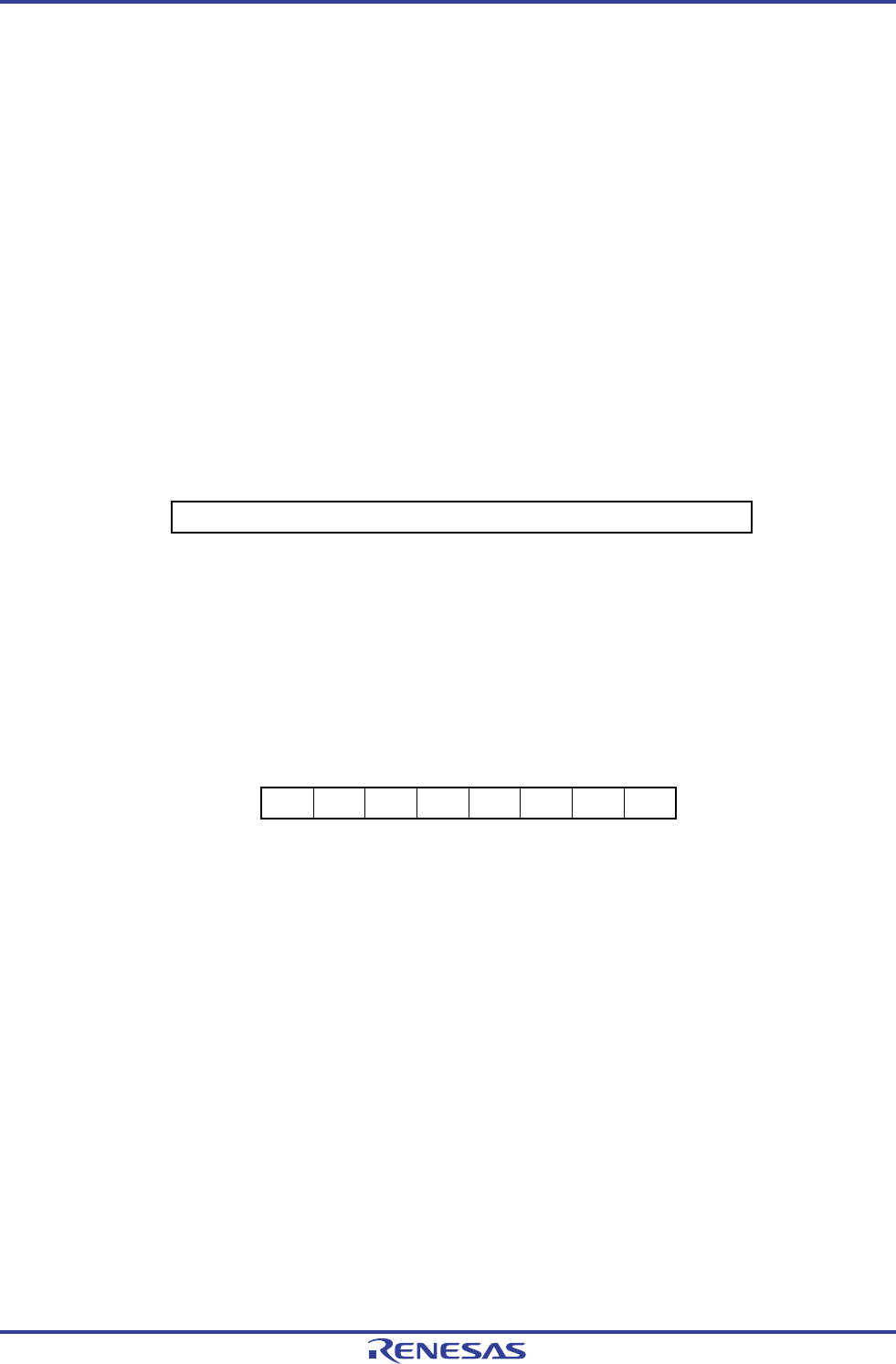

(1) Program counter (PC)

The program counter is a 20-bit register that holds the address information of the next program to be executed.

In normal operation, PC is automatically incremented according to the number of bytes of the instruction to be fetched.

When a branch instruction is executed, immediate data and register contents are set.

Reset signal generation sets the reset vector table values at addresses 0000H and 0001H to the 16 lower-order bits

of the program counter. The four higher-order bits of the program counter are cleared to 0000.

Figure 3-7. Format of Program Counter

19

PC

0

(2) Program status word (PSW)

The program status word is an 8-bit register consisting of various flags set/reset by instruction execution.

Program status word contents are stored in the stack area upon vectored interrupt request is acknowledged or PUSH

PSW instruction execution and are restored upon execution of the RETB, RETI and POP PSW instructions. Reset

signal generation sets the PSW register to 06H.

Figure 3-8. Format of Program Status Word

IE Z RBS1 AC RBS0 ISP0 CY

70

ISP1PSW

(a) Interrupt enable flag (IE)

This flag controls the interrupt request acknowledge operations of the CPU.

When 0, the IE flag is set to the interrupt disabled (DI) state, and all maskable interrupt requests are disabled.

When 1, the IE flag is set to the interrupt enabled (EI) state and maskable interrupt request acknowledgment is

controlled with an in-service priority flag (ISP1, ISP0), an interrupt mask flag for various interrupt sources, and a

priority specification flag.

The IE flag is reset (0) upon DI instruction execution or interrupt acknowledgment and is set (1) upon EI

instruction execution.

(b) Zero flag (Z)

When the operation or comparison result is zero or equal, this flag is set (1). It is reset (0) in all other cases.

(c) Register bank select flags (RBS0, RBS1)

These are 2-bit flags to select one of the four register banks.

In these flags, the 2-bit information that indicates the register bank selected by SEL RBn instruction execution is

stored.