RL78/G1A CHAPTER 3 CPU ARCHITECTURE

R01UH0305EJ0200 Rev.2.00 66

Jul 04, 2013

3.2.4 Special function registers (SFRs)

Unlike a general-purpose register, each SFR has a special function.

SFRs are allocated to the FFF00H to FFFFFH area.

SFRs can be manipulated like general-purpose registers, using operation, transfer, and bit manipulation instructions.

The manipulable bit units, 1, 8, and 16, depend on the SFR type.

Each manipulation bit unit can be specified as follows.

• 1-bit manipulation

Describe as follows for the 1-bit manipulation instruction operand (sfr.bit).

When the bit name is defined: <Bit name>

When the bit name is not defined: <Register name>.<Bit number> or <Address>.<Bit number>

• 8-bit manipulation

Describe the symbol defined by the assembler for the 8-bit manipulation instruction operand (sfr). This manipulation

can also be specified with an address.

• 16-bit manipulation

Describe the symbol defined by the assembler for the 16-bit manipulation instruction operand (sfrp). When

specifying an address, describe an even address.

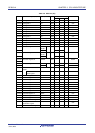

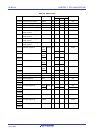

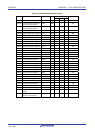

Table 3-5 gives a list of the SFRs. The meanings of items in the table are as follows.

• Symbol

Symbol indicating the address of a special function register. It is a reserved word in the assembler, and is defined

as an sfr variable using the #pragma sfr directive in the compiler. When using the assembler, debugger, and

simulator, symbols can be written as an instruction operand.

• R/W

Indicates whether the corresponding SFR can be read or written.

R/W: Read/write enable

R: Read only

W: Write only

• Manipulable bit units

“√” indicates the manipulable bit unit (1, 8, or 16). “−” indicates a bit unit for which manipulation is not possible.

• After reset

Indicates each register status upon reset signal generation.

Caution Do not access addresses to which extended SFRs are not assigned.

Remark For extended SFRs (2nd SFRs), see 3.2.5 Extended special function registers (2nd SFRs: 2nd Special

Function Registers).