RL78/G1A CHAPTER 13 SERIAL INTERFACE IICA

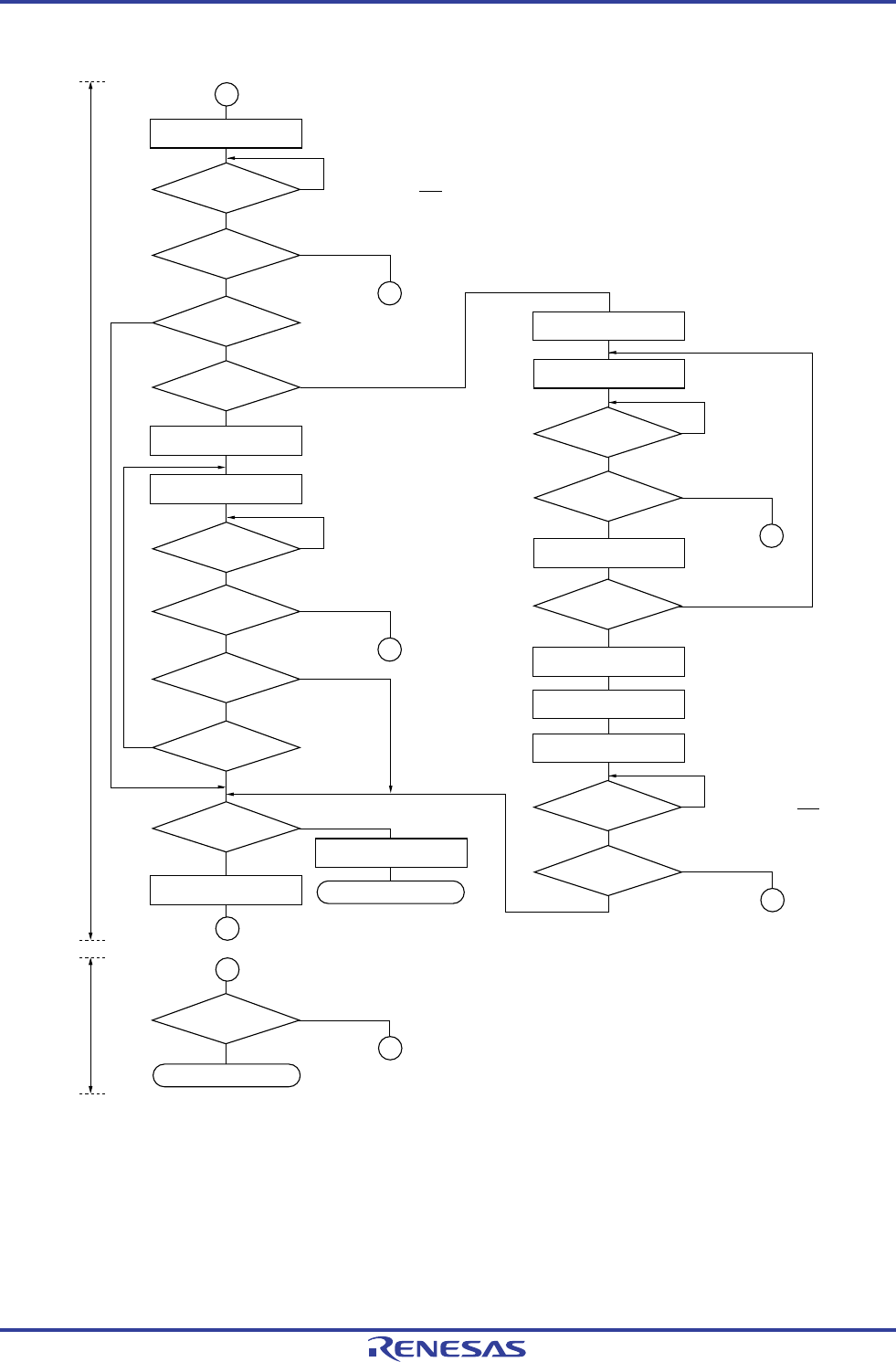

Figure 13-29. Master Operation in Multi-Master System (4/4)

Writing IICAn

WTIMn = 1

WRELn = 1

Reading IICAn

ACKEn = 1

WTIMn = 0

ACKEn = 0

WTIMn = 1

WRELn = 1

Writing IICAn

Yes

TRCn = 1?

Restart?

MSTSn = 1?

Starts communication

(specifies an address and transfer direction).

Starts transmission.

No

Yes

Waits for data reception.

Starts reception.

Yes

No

INTIICAn

interrupt occurs?

Yes

No

Transfer end?

Waits for detection of ACK.

Yes

No

INTIICAn

interrupt occurs?

Waits for data transmission.

Does not participate

in communication.

Yes

No

INTIICAn

interrupt occurs?

No

Yes

ACKDn = 1?

No

Yes

No

C

2

Yes

MSTSn = 1?

No

Yes

Transfer end?

No

Yes

ACKDn = 1?

No

2

Yes

MSTSn = 1?

No

2

Waits for detection of ACK.

Yes

No

INTIICAn

interrupt occurs?

Yes

MSTSn = 1?

No

C

2

Yes

EXCn = 1 or COIn = 1?

No

1

2

SPTn = 1

STTn = 1

Slave operation

END

Communication processingCommunication processing

<R>

<R>

<R>

Remarks 1. Conform to the specifications of the product that is communicating, with respect to the transmission and

reception formats.

2. To use the device as a master in a multi-master system, read the MSTS0 bit each time interrupt INTIICA0

has occurred to check the arbitration result.

3. To use the device as a slave in a multi-master system, check the status by using the IICA status register

0 (IICS0) and IICA flag register 0 (IICF0) each time interrupt INTIICA0 has occurred, and determine the

processing to be performed next.

4. n = 0

R01UH0305EJ0200 Rev.2.00 613

Jul 04, 2013