RL78/G1A CHAPTER 6 TIMER ARRAY UNIT

R01UH0305EJ0200 Rev.2.00 225

Jul 04, 2013

6.5.3 Operation of counter

Here, the counter operation in each mode is explained.

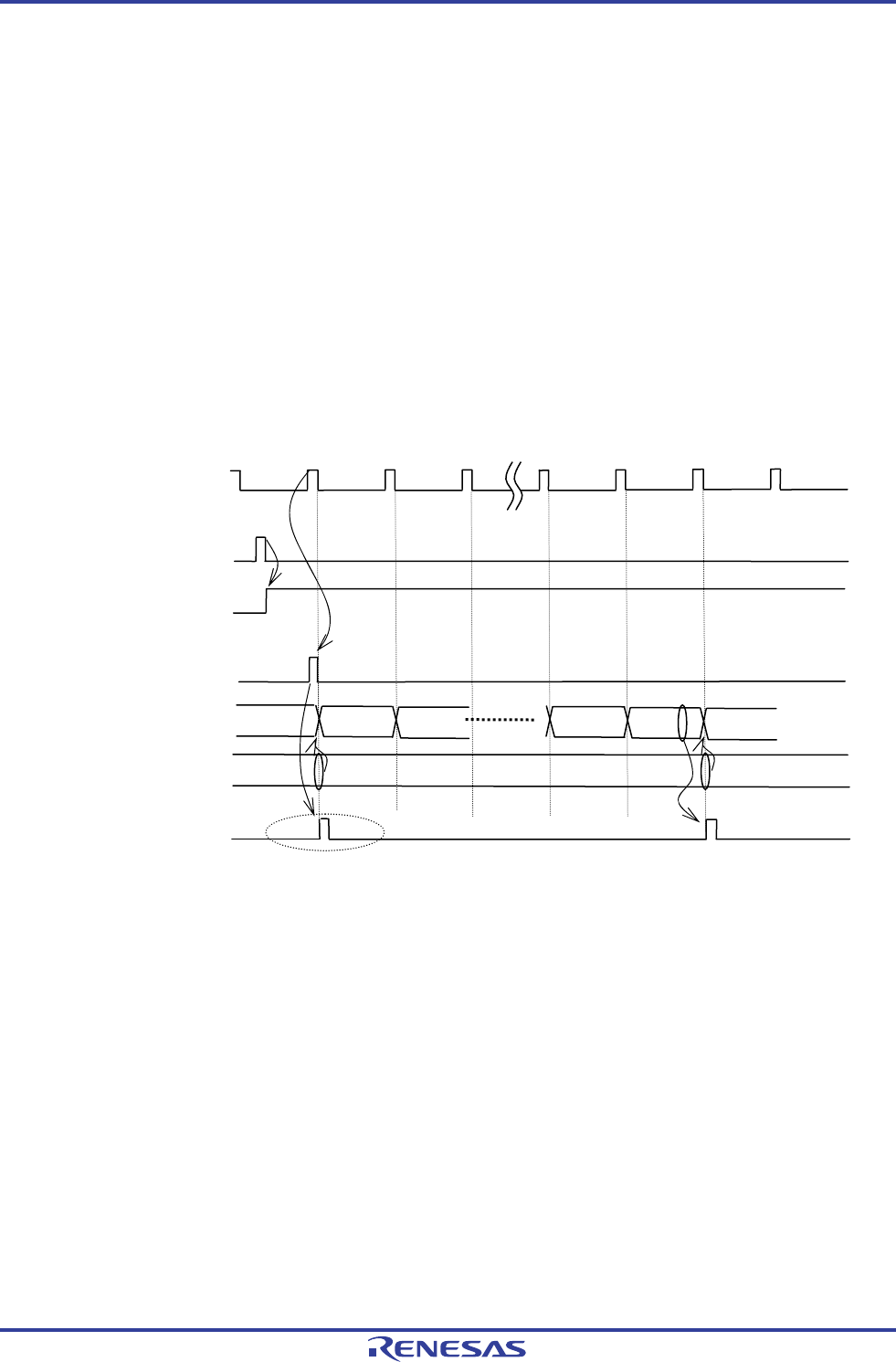

(1) Operation of interval timer mode

<1> Operation is enabled (TEmn = 1) by writing 1 to the TSmn bit. Timer count register mn (TCRmn) holds the

initial value until count clock generation.

<2> A start trigger is generated at the first count clock after operation is enabled.

<3> When the MDmn0 bit is set to 1, INTTMmn is generated by the start trigger.

<4> By the first count clock after the operation enable, the value of timer data register mn (TDRmn) is loaded to the

TCRmn register and counting starts in the interval timer mode.

<5> When the TCRmn register counts down and its count value is 0000H, INTTMmn is generated and the value of

timer data register mn (TDRmn) is loaded to the TCRmn register and counting keeps on.

Figure 6-25. Operation Timing (In Interval Timer Mode)

Caution In the operation in the first count clock cycle after writing the TSmn bit, an error at a maximum of

one count clock cycle occurs since count start delays until count clock has been generated.

When the information on count start timing is necessary, an interrupt can be generated when

counting is started by setting MDmn0 = 1.

Remarks 1. f

MCK, the start trigger detection signal, and INTTMmn become active between one clock in

synchronization with fCLK.

2. m: Unit number (m = 0), n: Channel number (n = 0 to 7 (however, timer input pin (TImn), timer output

pin (TOmn) : n = 0, 1, 3 to 7))

fMCK

(fTCLK)

m

TSmn (write)

TEmn

Start trigger

detection signal

TCRmn

Initial

value

m

TDRmn

INTTMmn

When MDmn0 = 1 setting

<1>

<3>

<4>

m−1

0000

m

0001

<2>

<5>