RL78/G1A CHAPTER 16 INTERRUPT FUNCTIONS

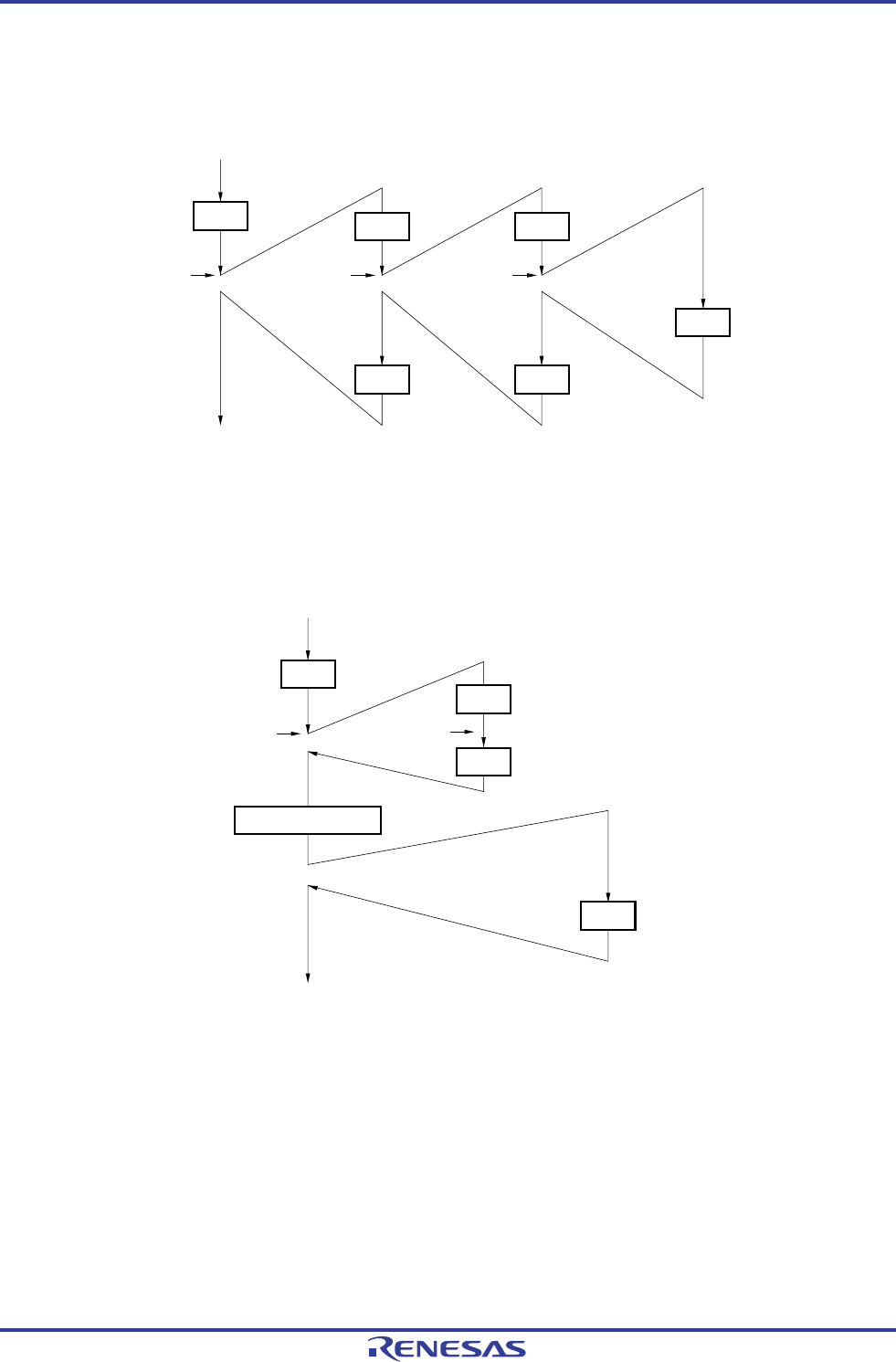

Figure 16-10. Examples of Multiple Interrupt Servicing (1/2)

Example 1. Multiple interrupt servicing occurs twice

Main processing INTxx servicing INTyy servicing INTzz servicing

EI

EI

EI

RETI RETI

RETI

INTxx

(PR = 11)

INTyy

(PR = 10)

INTzz

(PR = 01)

IE = 0 IE = 0 IE = 0

IE = 1 IE = 1

IE = 1

During servicing of interrupt INTxx, two interrupt requests, INTyy and INTzz, are acknowledged, and multiple interrupt

servicing takes place. Before each interrupt request is acknowledged, the EI instruction must always be issued to enable

interrupt request acknowledgment.

Example 2. Multiple interrupt servicing does not occur due to priority control

Main processing INTxx servicing INTyy servicing

INTxx

(PR = 10)

INTyy

(PR = 11)

EI

RETI

IE = 0

IE = 0

EI

1 instruction execution

RETI

IE = 1

IE = 1

Interrupt request INTyy issued during servicing of interrupt INTxx is not acknowledged because its priority is lower than

that of INTxx, and multiple interrupt servicing does not take place. The INTyy interrupt request is held pending, and is

acknowledged following execution of one main processing instruction.

PR = 00: Specify level 0 with ××PR1× = 0, ××PR0× = 0 (higher priority level)

PR = 01: Specify level 1 with ××PR1× = 0, ××PR0× = 1

PR = 10: Specify level 2 with ××PR1× = 1, ××PR0× = 0

PR = 11: Specify level 3 with ××PR1× = 1, ××PR0× = 1 (lower priority level)

IE = 0: Interrupt request acknowledgment is disabled

IE = 1: Interrupt request acknowledgment is enabled.

R01UH0305EJ0200 Rev.2.00 711

Jul 04, 2013