RL78/G1A CHAPTER 3 CPU ARCHITECTURE

R01UH0305EJ0200 Rev.2.00 55

Jul 04, 2013

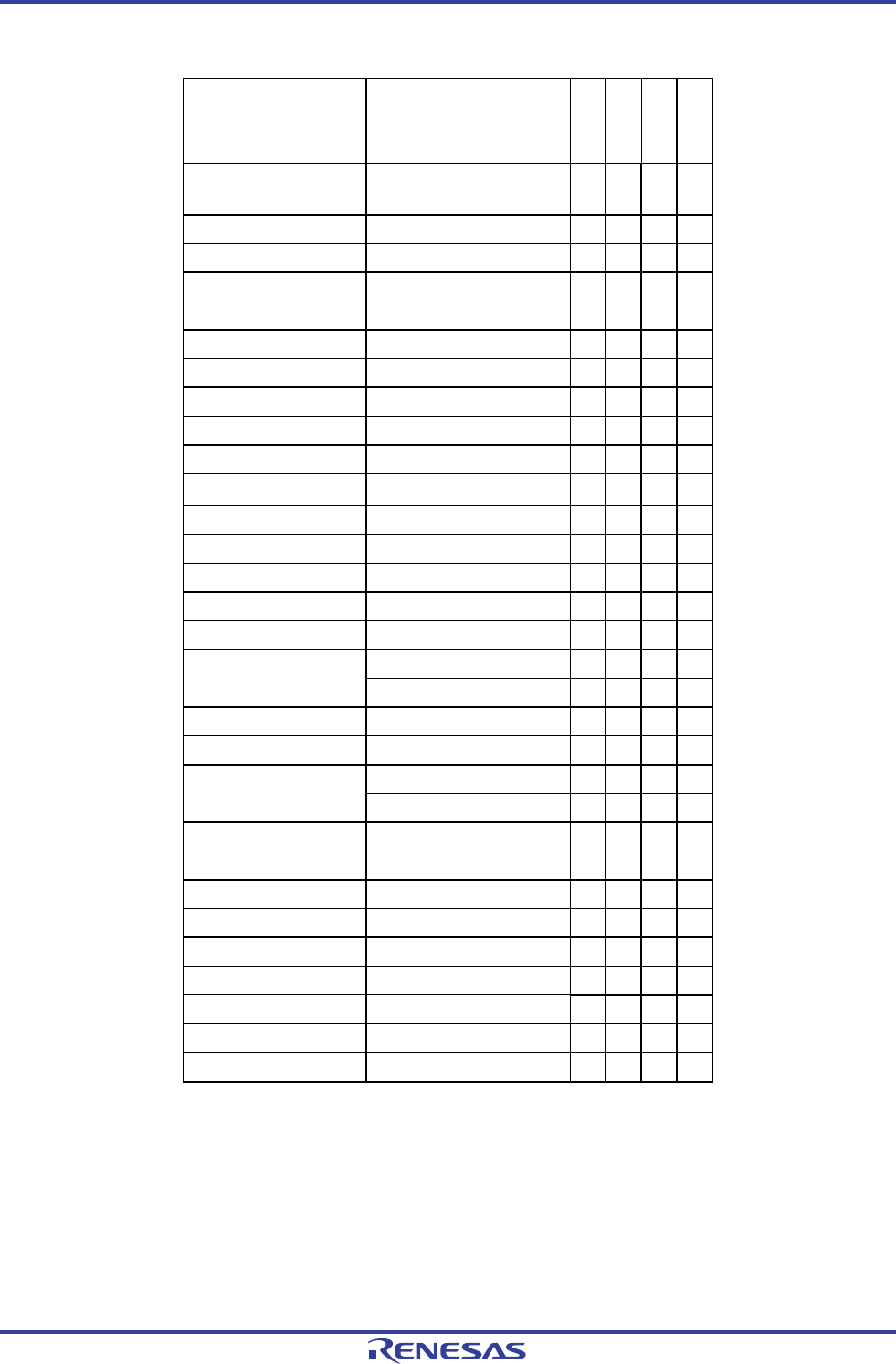

Table 3-3. Vector Table (1/2)

Vector Table Address Interrupt Source

64-pin

48-pin

32-pin

25-pin

0000H

RESET, POR, LVD, WDT,

TRAP, IAW, RPE

√ √ √ √

0004H INTWDTI/INTSRO

√ √ √ √

0006H INTLVI

√ √ √ √

0008H INTP0

√ √ √ √

000AH INTP1

√ √ √ √

000CH INTP2

√ √ √ √

000EH INTP3

√ √ √ √

0010H INTP4

√ √ √ √

0012H INTP5

√ √ − −

0014H INTST2/INTCSI20/INTIIC20

√ √ √ −

0016H INTSR2/INTCSI21/INTIIC21

√ √

Note 1

−

0018H INTSRE2

√ √ √ −

001AH INTDMA0

√ √ √ √

001CH INTDMA1

√ √ √ √

001EH INTST0/INTCSI00/INTIIC00

√ √ √ √

0020H INTSR0/INTCSI01/INTIIC01

√ √

Note 2 Note 2

0022H INTSRE0

√ √ √ √

INTTM01H

√ √ √ √

0024H INTST1/INTCSI10/INTIIC10

√

Note 3 Note 3 Note 3

0026H INTSR1/INTCSI11/INTIIC11

√ √ √ √

0028H INTSRE1

√ √ √ √

INTTM03H

√ √ √ √

002AH INTIICA0

√ √ √ √

002CH INTTM00

√ √ √ √

002EH INTTM01

√ √ √ √

0030H INTTM02

√ √ √ √

0032H INTTM03

√ √ √ √

0034H INTAD

√ √ √ √

0036H INTRTC

√ √ √ √

0038H INTIT

√ √ √ √

003AH INTKR

√ √ √

Note 4

Notes 1. INTSR2 only.

2. INTSR0 only.

3. INTSR1 only.

4. When setting the peripheral I/O redirection register (PIOR).