RL78/G1A CHAPTER 6 TIMER ARRAY UNIT

R01UH0305EJ0200 Rev.2.00 193

Jul 04, 2013

6.2.1 Timer count register mn (TCRmn)

The TCRmn register is a 16-bit read-only register and is used to count clocks.

The value of this counter is incremented or decremented in synchronization with the rising edge of a count clock.

Whether the counter is incremented or decremented depends on the operation mode that is selected by the MDmn3 to

MDmn0 bits of timer mode register mn (TMRmn) (see 6.3.3 Timer mode register mn (TMRmn)).

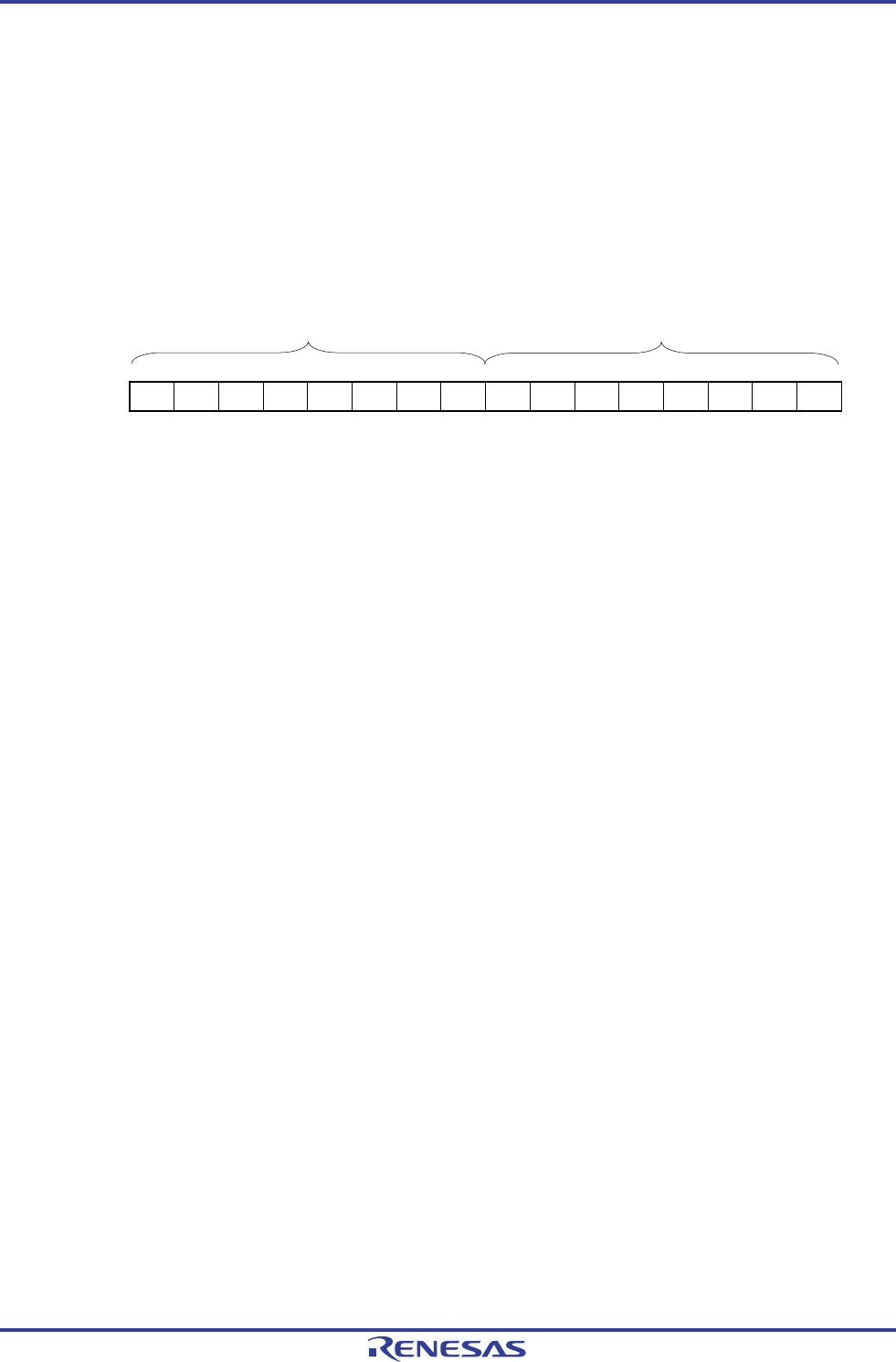

Figure 6-6. Format of Timer Count Register mn (TCRmn)

Address: F0180H, F0181H (TCR00) to F018EH, F018FH (TCR07), After reset: FFFFH R

F01C0H, F01C1H (TCR10) to F01CEH, F01CFH (TCR17)

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

TCRmn

Remark m: Unit number (m = 0), n: Channel number (n = 0 to 7)

The count value can be read by reading timer count register mn (TCRmn).

The count value is set to FFFFH in the following cases.

• When the reset signal is generated

• When the TAUmEN bit of peripheral enable register 0 (PER0) is cleared

• When counting of the slave channel has been completed in the PWM output mode

• When counting of the slave channel has been completed in the delay count mode

• When counting of the master/slave channel has been completed in the one-shot pulse output mode

• When counting of the slave channel has been completed in the multiple PWM output mode

The count value is cleared to 0000H in the following cases.

• When the start trigger is input in the capture mode

• When capturing has been completed in the capture mode

Caution The count value is not captured to timer data register mn (TDRmn) even when the TCRmn

register is read.

F0181H (TCR00)

F0180H (TCR00)