RL78/G1A CHAPTER 11 A/D CONVERTER

R01UH0305EJ0200 Rev.2.00 359

Jul 04, 2013

11.3.3 A/D converter mode register 1 (ADM1)

This register is used to specify the A/D conversion trigger, conversion mode, and hardware trigger signal.

The ADM1 register can be set by a 1-bit or 8-bit memory manipulation instruction.

Reset signal generation clears this register to 00H.

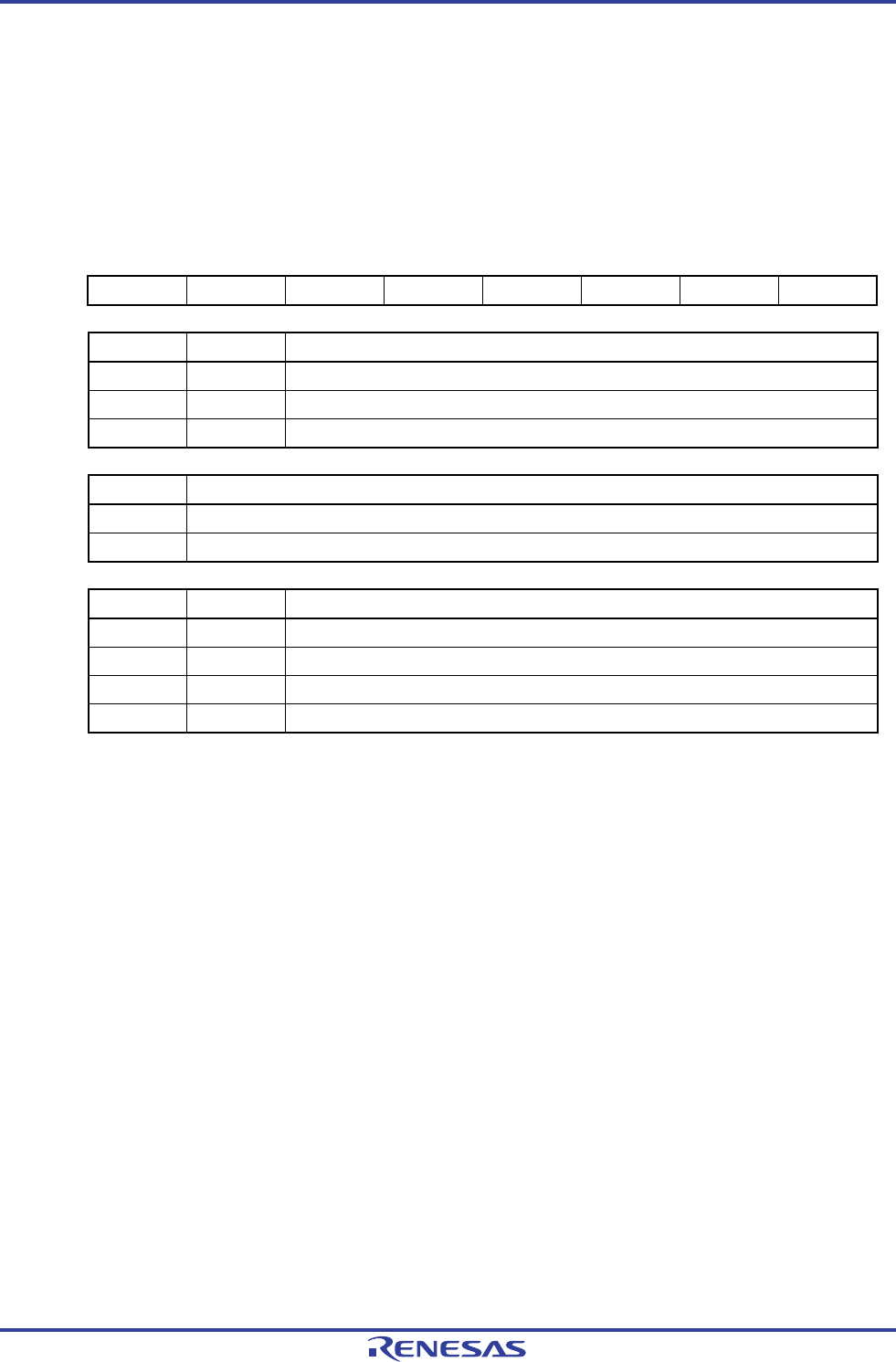

Figure 11-6. Format of A/D Converter Mode Register 1 (ADM1)

Address: FFF32H After reset: 00H R/W

Symbol 7 6 5 4 3 2 1 0

ADM1 ADTMD1 ADTMD0 ADSCM 0 0 0 ADTRS1 ADTRS0

ADTMD1 ADTMD0 Selection of the A/D conversion trigger mode

0

×

Software trigger mode

1 0 Hardware trigger no-wait mode

1 1 Hardware trigger wait mode

ADSCM Specification of the A/D conversion mode

0 Sequential conversion mode

1 One-shot conversion mode

ADTRS1 ADTRS0 Selection of the hardware trigger signal

0 0 End of timer channel 01 count or capture interrupt signal (INTTM01)

0 1 Setting prohibited

1 0 Real-time clock interrupt signal (INTRTC)

1 1 Interval timer interrupt signal (INTIT)

Cautions 1. Rewrite the value of the ADM1 register while conversion is stopped (ADCS = 0, ADCE = 0).

2. To complete A/D conversion, specify at least the following time as the hardware trigger interval:

Hardware trigger no wait mode: 2 f

CLK clock + A/D conversion time

Hardware trigger wait mode: 2 f

CLK clock + A/D power supply stabilization wait time +

A/D conversion time

3. In modes other than SNOOZE mode, input of the next INTRTC or INTIT will not be recognized as

a valid hardware trigger for up to four f

CLK cycles after the first INTRTC or INTIT is input.

Remarks 1. ×: don’t care

2. f

CLK: CPU/peripheral hardware clock frequency

<R>

<R>