RL78/G1A CHAPTER 5 CLOCK GENERATOR

R01UH0305EJ0200 Rev.2.00 156

Jul 04, 2013

5.3.8 High-speed on-chip oscillator frequency select register (HOCODIV)

The frequency of the high-speed on-chip oscillator which is set by an option byte (000C2H) can be changed by using

high-speed on-chip oscillator frequency select register (HOCODIV). However, the selectable frequency depends on the

FRQSEL3 bit of the option byte (000C2H).

The HOCODIV register can be set by an 8-bit memory manipulation instruction.

Reset signal generation clears this register to the value set by FRQSEL2 to FRQSEL0 of the option byte (000C2H).

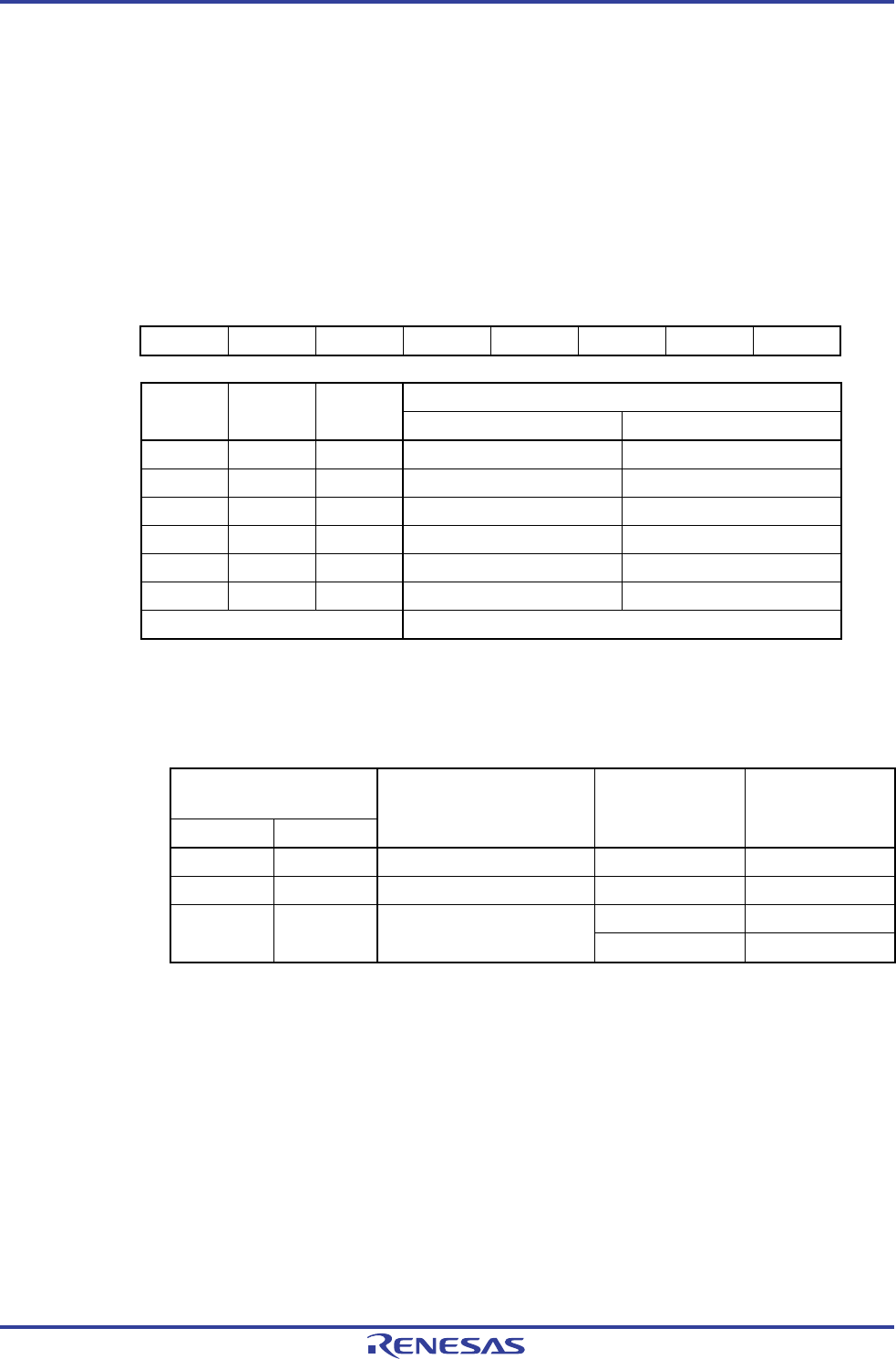

Figure 5-9. Format of High-speed On-chip Oscillator Frequency Select Register (HOCODIV)

Address: F00A8H After reset: the value set by FRQSEL2 to FRQSEL0 of the option byte (000C2H) R/W

Symbol 7 6 5 4 3 2 1 0

HOCODIV

0 0 0 0 0 HOCODIV2 HOCODIV1 HOCODIV0

High-Speed On-Chip Oscillator Clock Frequency

HOCODIV2 HOCODIV1 HOCODIV0

FRQSEL3 Bit is 0 FRQSEL3 Bit of is 1

0 0 0 24 MHz 32 MHz

0 0 1 12 MHz 16 MHz

0 1 0 6 MHz 8 MHz

0 1 1 3 MHz 4 MHz

1 0 0 Setting prohibited 2 MHz

1 0 1 Setting prohibited 1 MHz

Other than aboves Setting prohibited

Cautions 1. When changing the frequency by using the HOCODIV register, specify a

frequency in the voltage range corresponding to the flash operating mode

specified in the option byte (000C2H).

Option Byte (000C2H)

Value

CMODE1 CMODE0

Flash Operation Mode

Operating

Frequency Range

Operating Voltage

Range

0 0 LV (low-voltage main) mode 1 to 4 MHz 1.6 to 3.6 V

1 0 LS (low-speed main) mode 1 to 8 MHz 1.8 to 3.6 V

1 to 16 MHz 2.4 to 3.6 V 1 1 HS (high-speed main) mode

1 to 32 MHz 2.7 to 3.6 V

2. Change the HOCODIV register value while the high-speed on-chip oscillator clock

(f

IH) is selected as the CPU/peripheral hardware clock (fCLK).

3. After the frequency is changed using the HOCODIV register, the new frequency is

applied after the period below has elapsed.

- Operation for up to three clocks at the pre-change frequency

- CPU/peripheral hardware clock wait at the post-change frequency for up to three

clocks

<R>

<R>