RL78/G1A CHAPTER 18 STANDBY FUNCTION

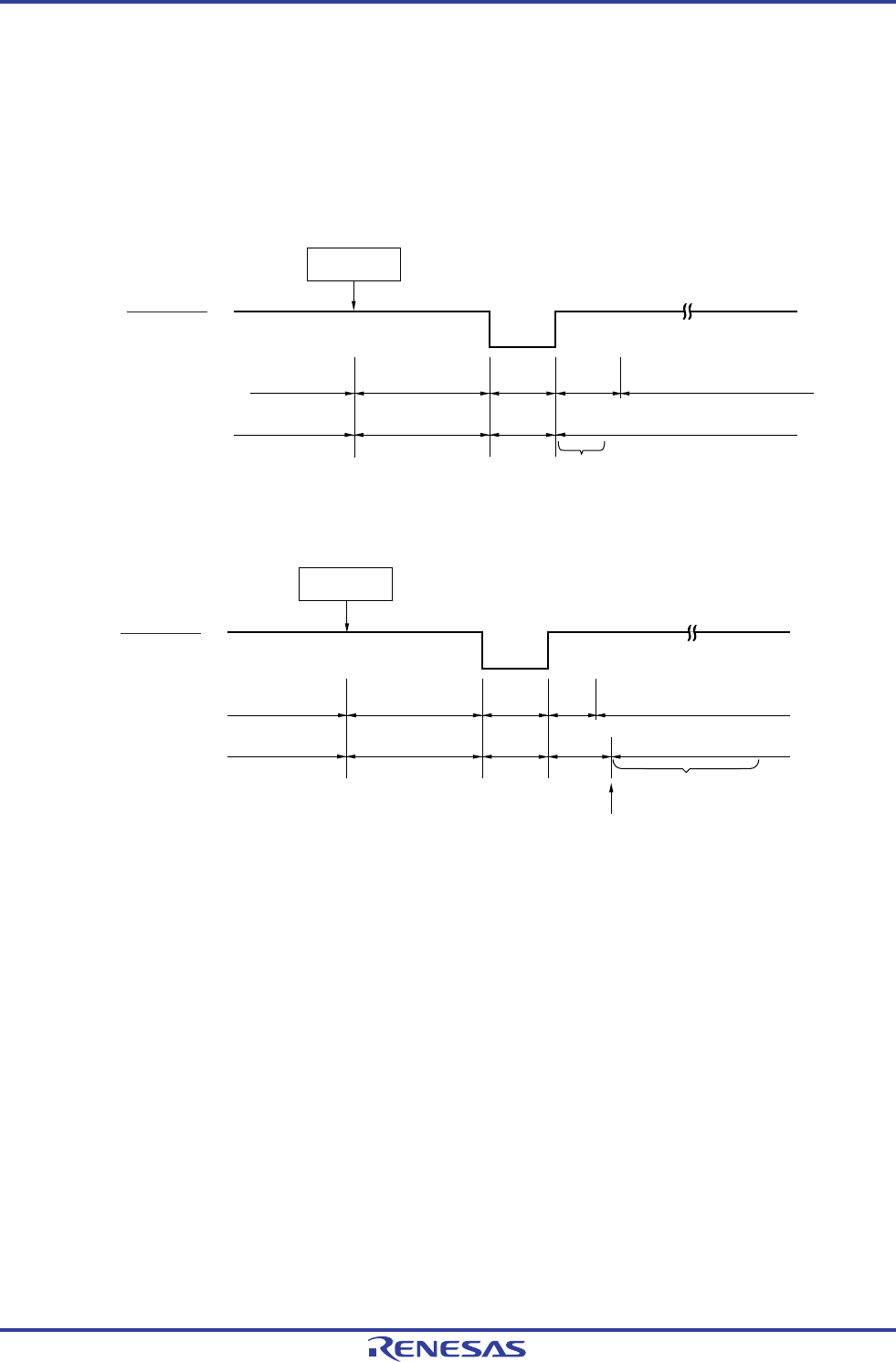

(b) Release by reset signal generation

When the reset signal is generated, STOP mode is released, and then, as in the case with a normal reset

operation, the program is executed after branching to the reset vector address.

Figure 18-4. STOP Mode Release by Reset

(1) When high-speed on-chip oscillator clock is used as CPU clock

<R>

STOP

instruction

Reset signal

High-speed on-chip

oscillator clock

STOP mode

Reset

period

Oscillates

Oscillation

stopped

Status of CPU

Normal operation

(high-speed on-chip

oscillator clock)

Normal operation

(high-speed on-chip

oscillator clock)

Oscillates

Oscillation stopped

Wait for oscillation

accuracy stabilization

Note

(2) When high-speed system clock is used as CPU clock

<R>

STOP

instruction

Reset signal

High-speed system

clock (X1 oscillation)

STOP mode

Reset

period

Oscillates

Oscillation

stopped

Oscillates

Status of CPU

Normal operation

(high-speed

system clock)

Normal operation

(high-speed on-chip

oscillator clock)

Oscillation

stopped

Oscillation stopped

Oscillation stabilization time

(check by using OSTC register)

Starting X1 oscillation is

specified by software.

Note

<R>

Note For the reset processing time, see CHAPTER 19 RESET FUNCTION. For the reset processing time of

the power-on-reset circuit (POR) and voltage detector (LVD), see CHAPTER 20 POWER-ON-RESET

CIRCUIT.

R01UH0305EJ0200 Rev.2.00 736

Jul 04, 2013