RL78/G1A CHAPTER 13 SERIAL INTERFACE IICA

13.2 Configuration of Serial Interface IICA

Serial interface IICA includes the following hardware.

Table 13-1. Configuration of Serial Interface IICA

Item Configuration

Registers IICA shift register 0 (IICA0)

Slave address register 0 (SVA0)

Control registers Peripheral enable register 0 (PER0)

IICA control register 00 (IICCTL00)

IICA status register 0 (IICS0)

IICA flag register 0 (IICF0)

IICA control register 01 (IICCTL01)

IICA low-level width setting register 0 (IICWL0)

IICA high-level width setting register 0 (IICWH0)

Port mode register 6 (PM6)

Port register 6 (P6)

(1) IICA shift register 0 (IICA0)

The IICA0 register is used to convert 8-bit serial data to 8-bit parallel data and vice versa in synchronization with

the serial clock. The IICA0 register can be used for both transmission and reception.

The actual transmit and receive operations can be controlled by writing and reading operations to the IICA0 register.

Cancel the wait state and start data transfer by writing data to the IICA0 register during the wait period.

The IICA0 register can be set by an 8-bit memory manipulation instruction.

Reset signal generation clears IICA0 to 00H.

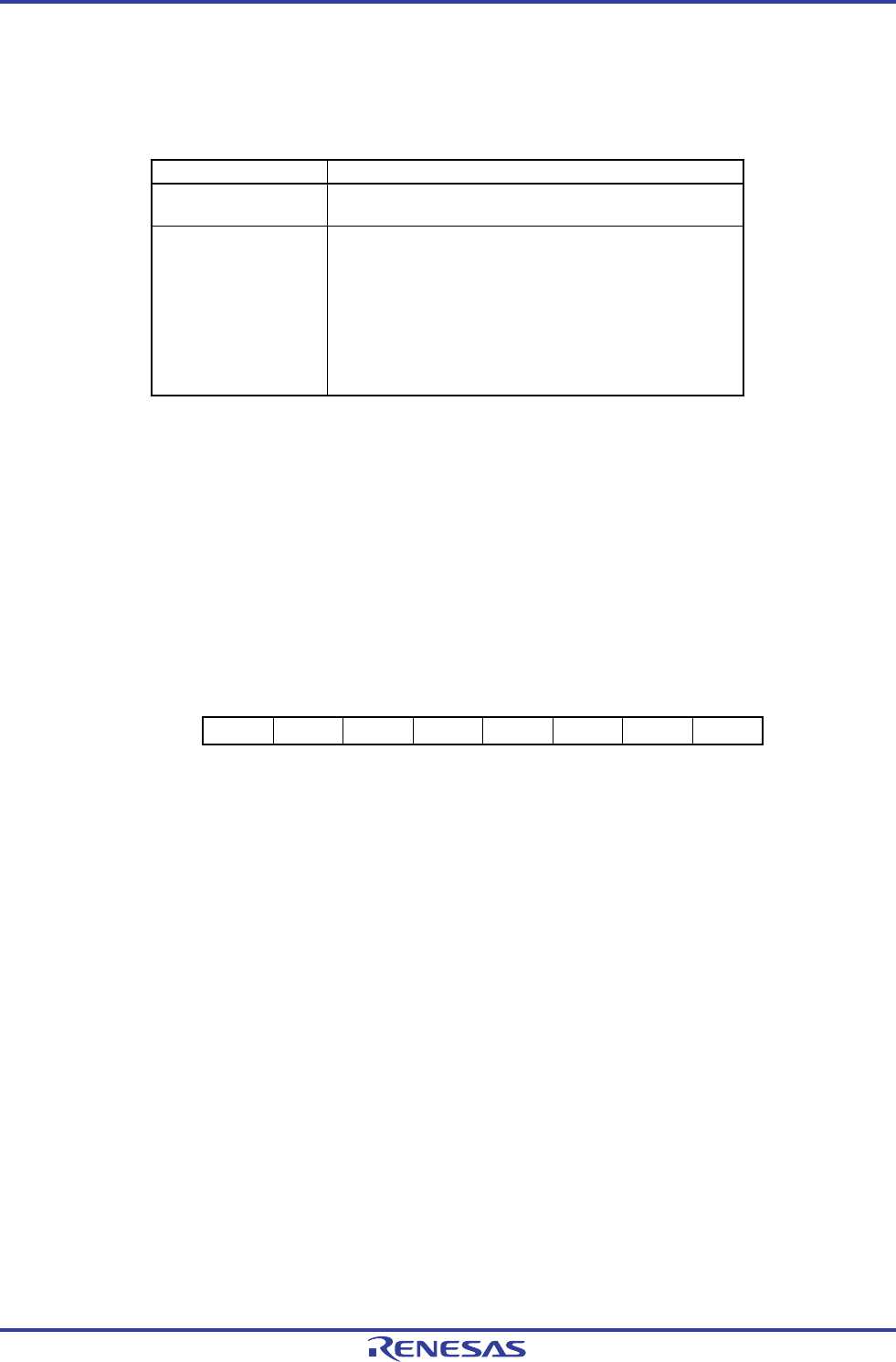

Figure 13-3. Format of IICA Shift Register 0 (IICA0)

Symbol

IICA0

Address: FFF50H After reset: 00H R/W

76543210

Cautions 1. Do not write data to the IICA0 register during data transfer.

2. Write or read the IICA0 register only during the wait period. Accessing the IICA0 register in a

communication state other than during the wait period is prohibited. When the device serves

as the master, however, the IICA0 register can be written only once after the communication

trigger bit (STT0) is set to 1.

3. When communication is reserved, write data to the IICA0 register after the interrupt triggered

by a stop condition is detected.

(2) Slave address register 0 (SVA0)

This register stores seven bits of local addresses {A6, A5, A4, A3, A2, A1, A0} when in slave mode.

The SVA0 register can be set by an 8-bit memory manipulation instruction.

However, rewriting to this register is prohibited while STD0 = 1 (while the start condition is detected).

Reset signal generation clears the SVA0 register to 00H.

R01UH0305EJ0200 Rev.2.00 569

Jul 04, 2013