RL78/G1A CHAPTER 5 CLOCK GENERATOR

R01UH0305EJ0200 Rev.2.00 173

Jul 04, 2013

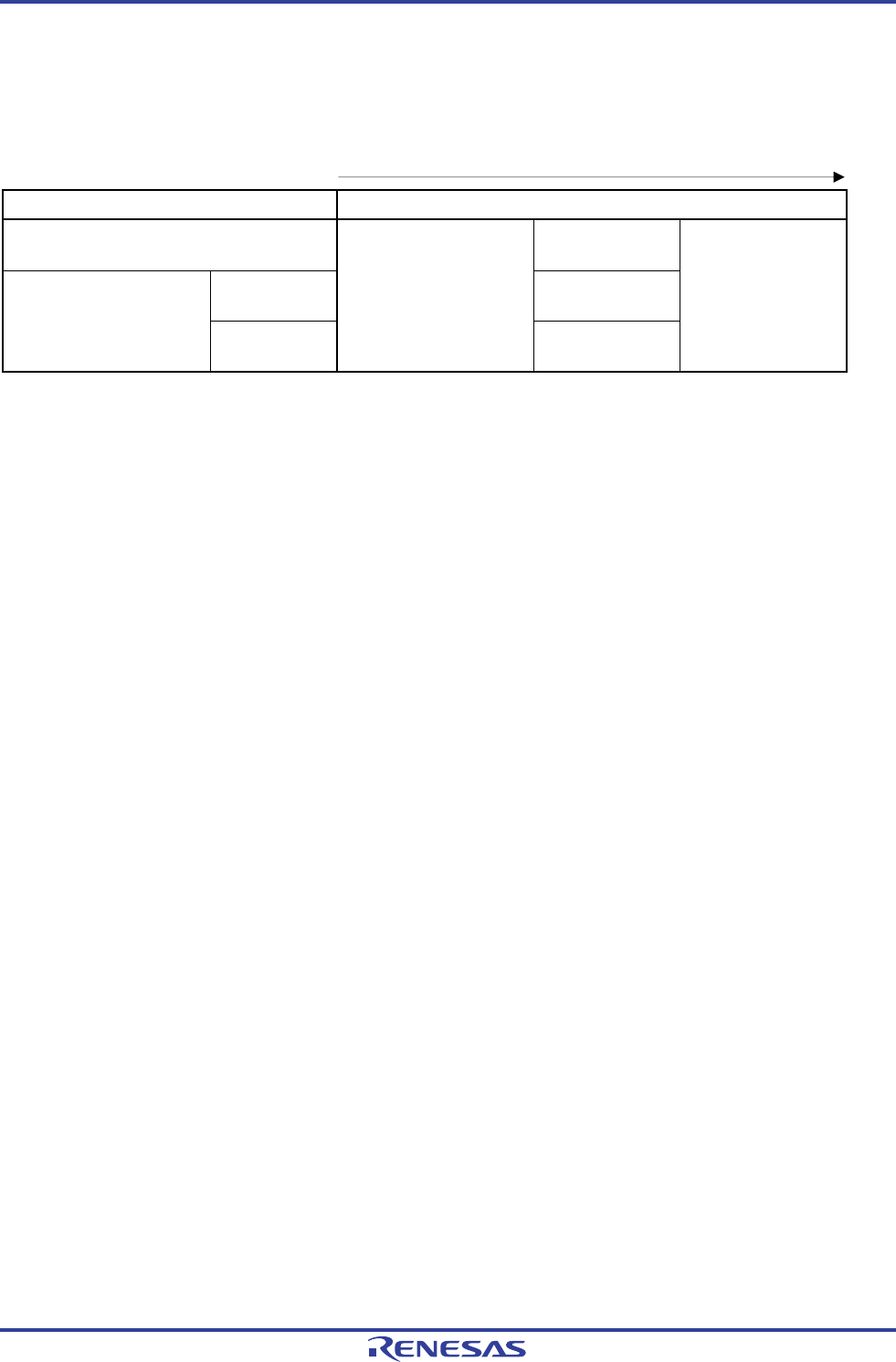

Table 5-3. CPU Clock Transition and SFR Register Setting Examples (5/5)

(11) • STOP mode (H) set while CPU is operating with high-speed on-chip oscillator clock (B)

• STOP mode (I) set while CPU is operating with high-speed system clock (C)

(Setting sequence)

Status Transition Setting

(B) → (H)

−

In X1 oscillation

Sets the OSTS

register

(C) → (I)

External main

system clock

Stopping peripheral

functions that are

disabled in STOP mode

−

Executing STOP

instruction

(12) CPU changing from STOP mode (H) to SNOOZE mode (J)

For details about the setting for switching from the STOP mode to the SNOOZE mode, see 11.8 SNOOZE Mode

Function, 12.5.7 SNOOZE mode function and 12.6.3 SNOOZE mode function.

Remark (A) to (J) in Table 5-3 correspond to (A) to (J) in Figure 5-15.

<R>