RL78/G1A CHAPTER 12 SERIAL ARRAY UNIT

R01UH0305EJ0200 Rev.2.00 548

Jul 04, 2013

(1) Register setting

Figure 12-103. Example of Contents of Registers for Address Field Transmission of Simplified I

2

C (IIC00, IIC01,

IIC10, IIC11, IIC20, IIC21) (1/2)

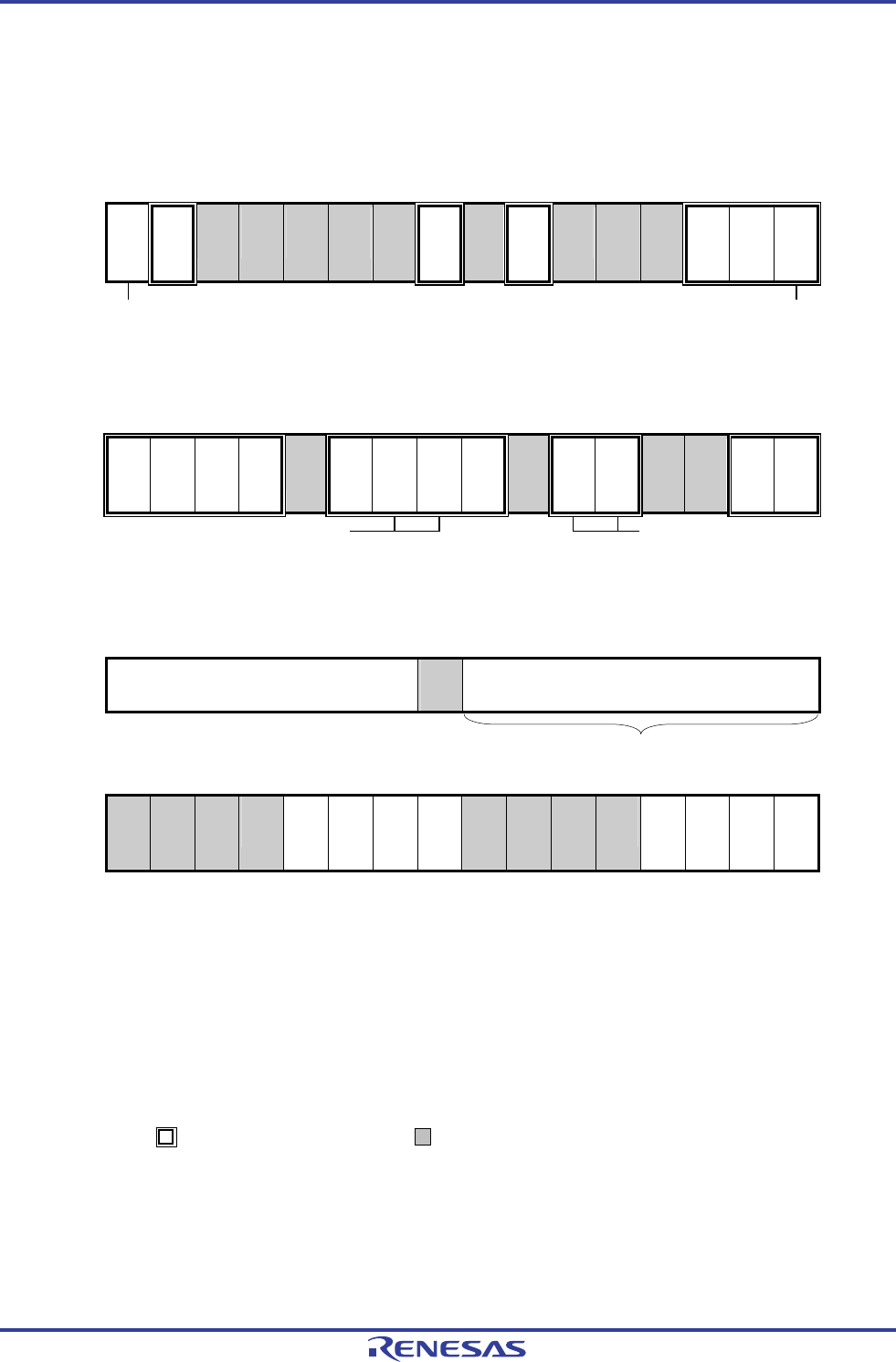

(a) Serial mode register mn (SMRmn)

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

SMRmn

CKSmn

0/1

CCSmn

0

0

0

0

0

0

STSmn

Note 1

0

0

SISmn0

Note 1

0

1

0

0

MDmn2

1

MDmn1

0

MDmn0

0

Operation clock (fMCK) of channel n

0: Prescaler output clock CKm0 set by the SPSm register

1: Prescaler output clock CKm1 set by the SPSm register

Operation mode of channel n

0: Transfer end interrupt

(b) Serial communication operation setting register mn (SCRmn)

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

SCRmn

TXEmn

1

RXEmn

0

DAPmn

0

CKPmn

0

0

EOCmn

0

PTCmn1

0

PTCmn0

0

DIRmn

0

0

SLCmn1

Note 2

0

SLCmn0

1

0

1

DLSmn1

1

Note 3

DLSmn0

1

Setting of parity bit

00B: No parity

Setting of stop bit

01B: Appending 1 bit (ACK)

(c) Serial data register mn (SDRmn) (lower 8 bits: SIOr)

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

SDRmn

Baud rate setting

0

Transmit data setting (address + R/W)

(d) Serial output register m (SOm)

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

SOm

0

0

0

0

CKOm3

0/1

Note 4

CKOm2

0/1

Note 4

CKOm1

0/1

CKOm0

0/1

0

0

0

0

SOm3

0/1

Note 4

SOm2

0/1

Note 4

SOm1

0/1

SOm0

0/1

Start condition is generated by manipulating the SOmn bit.

Notes 1. Only provided for the SMR01, SMR03, and SMR11 registers.

2. Only provided for the SCR00, SCR02, and SCR10 registers.

3. Only provided for the SCR00 and SCR01 registers. This bit is fixed to 1 for the other registers.

4. Unit 0 only

Remarks 1. m: Unit number (m = 0, 1), n: Channel number (n = 0 to 3), r: IIC number (r = 00, 01, 10, 11, 20, 21),

mn = 00 to 03, 10, 11

2. : Setting is fixed in the IIC mode, : Setting disabled (set to the initial value)

0/1: Set to 0 or 1 depending on the usage of the user

SIOr

<R>

<R>