RL78/G1A CHAPTER 16 INTERRUPT FUNCTIONS

16.4.4 Interrupt request hold

There are instructions where, even if an interrupt request is issued while the instructions are being executed, interrupt

request acknowledgment is held pending until the end of execution of the next instruction. These instructions (interrupt

request hold instructions) are listed below.

• MOV PSW, #byte

• MOV PSW, A

• MOV1 PSW. bit, CY

• SET1 PSW. bit

• CLR1 PSW. bit

• RETB

• RETI

• POP PSW

• BTCLR PSW. bit, $addr20

• EI

• DI

• SKC

• SKNC

• SKZ

• SKNZ

• SKH

• SKNH

• Write instructions for the IF0L, IF0H, IF1L, IF1H, IF2L, IF2H, MK0L, MK0H, MK1L, MK1H, MK2L, MK2H, PR00L,

PR00H, PR01L, PR01H, PR02L, PR02H, PR10L, PR10H, PR11L, PR11H, PR12L, and PR12H registers

<R>

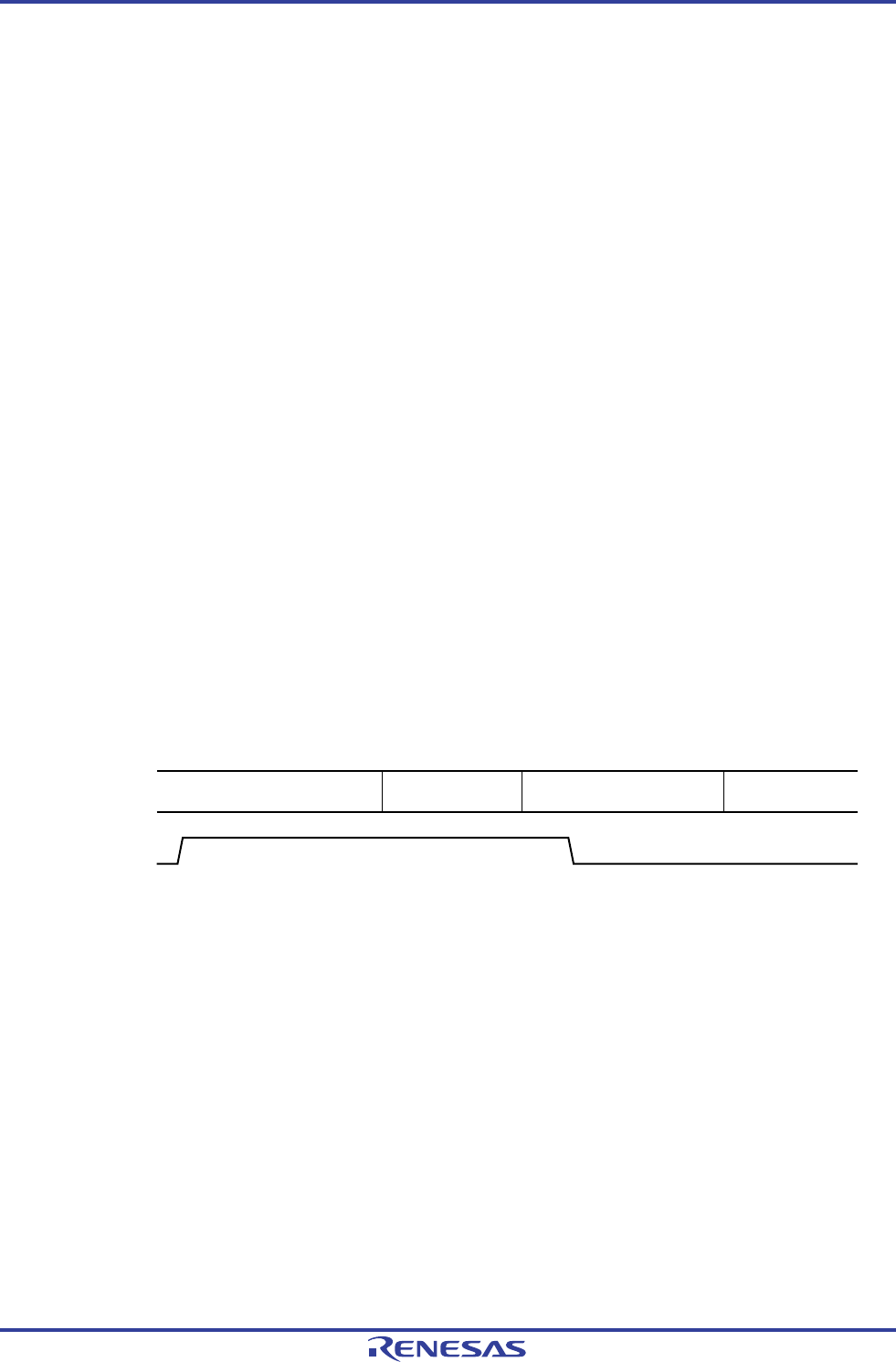

Figure 16-11 shows the timing at which interrupt requests are held pending.

Figure 16-11. Interrupt Request Hold

Instruction N Instruction M

PSW and PC saved, jump

to interrupt servicing

Interrupt servicing

program

CPU processing

××IF

Remarks 1. Instruction N: Interrupt request hold instruction

2. Instruction M: Instruction other than interrupt request hold instruction

R01UH0305EJ0200 Rev.2.00 713

Jul 04, 2013