RL78/G1A CHAPTER 12 SERIAL ARRAY UNIT

R01UH0305EJ0200 Rev.2.00 552

Jul 04, 2013

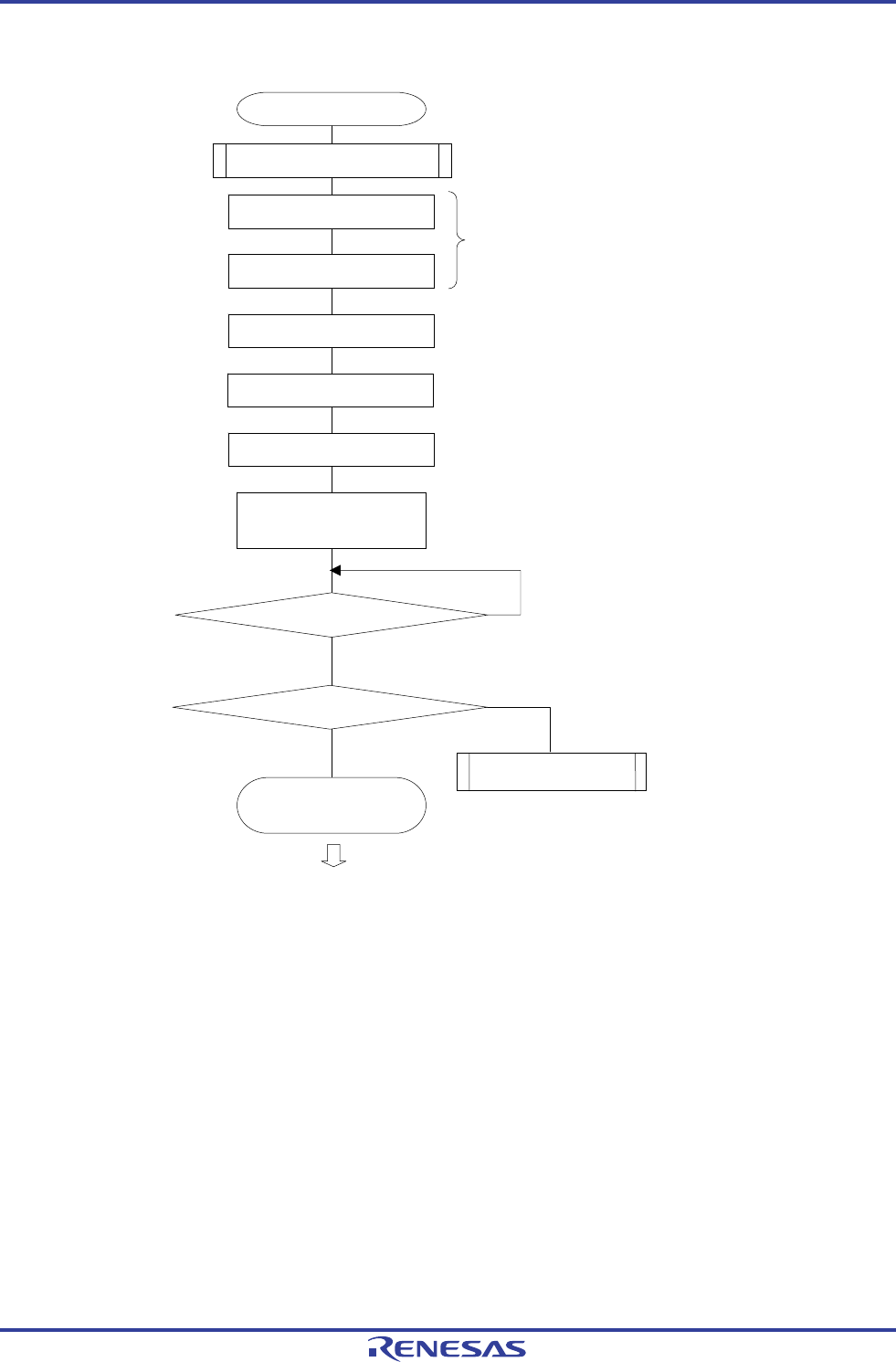

Figure 12-106. Flowchart of Simplified I

2

C Address Field Transmission

Remark m: Unit number (m = 0, 1), n: Channel number (n = 0 to 3), r: IIC number (r = 00, 01, 10, 11, 20, 21),

mn = 00 to 03, 10, 11

For the initial setting, see Figure 12-105.

No

Yes

Yes

Communication error

processing

To data transmission flow

and data reception flow

Writing 0 to the SOmn bit

Address field

transmission completed

Transfer end interrupt

g

enerated?

Writing address and R/W

data to SIOr (SDRmn[7:0])

Writing 1 to the SSmn bit

Responded ACK?

Writing 1 to the SOEmn bit

Writing 0 to the CKOmn bit

Default setting

Wait

No

Transmitting address field

Wait for address field transmission

complete.

(Clear the interrupt request flag)

Transmitting address field

To serial operation enable status

Enable serial output

Prepare to communicate the SCL signal is

fall

To secure a hold time of SCL signal

Start condition generate

Setting 0 of the SOmn bit

ACK response from the slave

will be confirmed in PEFmn bit.

if ACK (PEFmn = 0), to the next

processing, if NACK (PEFmn =

1) to error processing.