RL78/G1A CHAPTER 11 A/D CONVERTER

R01UH0305EJ0200 Rev.2.00 352

Jul 04, 2013

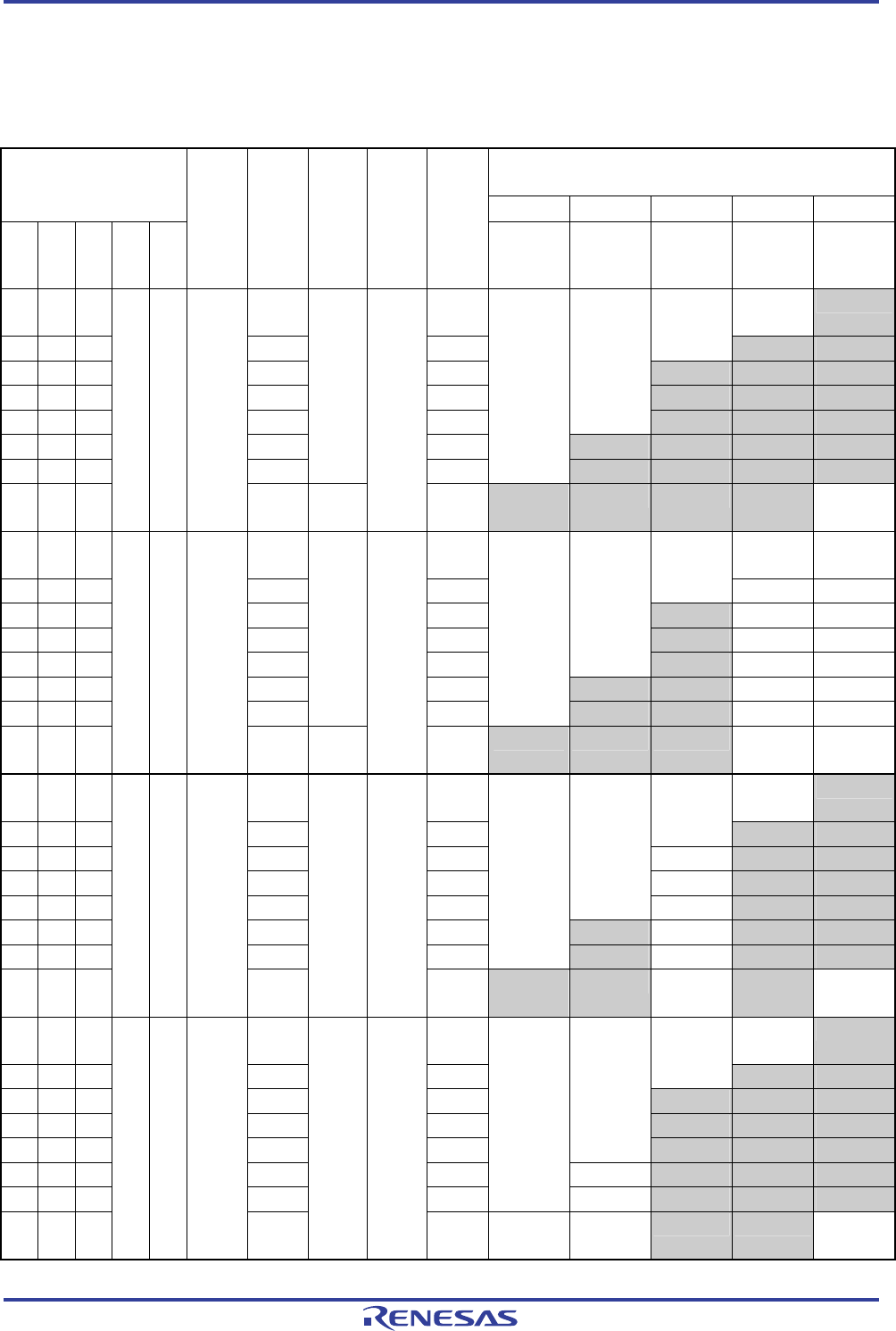

Table 11-3. A/D Conversion Time Selection (2/4)

(2) 12-bit resolution mode (ADTYP = 0) When there is A/D power supply stabilization wait time

(hardware trigger wait mode (except second and subsequent conversion in sequential conversion mode and conversion of

channel specified by scan 1, 2, and 3 in scan mode

Note 1

))

A/D Power Supply Stabilization Wait Time + Conversion Time

Selection

A/D Converter Mode Register

0 (ADM0)

AV

DD

= 1.6 to 3.6 V AV

DD

= 1.6 to 3.6 V AV

DD

= 1.8 to 3.6 V AV

DD

= 2.4 to 3.6 V AV

DD

= 2.7 to 3.6 V

FR2 FR1 FR0 LV1 LV0

Mode

Conversion

Clock (f

AD

)

Number of

A/D Power

Supply

Stabilization

Wait Clock

Number of

Conversion

Clock

A/D Power

Supply

Stabilization

Wait Time

+Conversion

Time

f

CLK

= 1 MHz f

CLK

= 4 MHz f

CLK

= 8 MHz f

CLK

= 16 MHz f

CLK

= 32 MHz

0 0 0 fCLK/32 1732/fCLK Setting

prohibited

54.125

μ

s

Note 2

0 0 1 fCLK/16 868/fCLK

Setting

prohibited

54.25

μ

s

Note 2

27.125

μ

s

Note 2

0 1 0 fCLK/8 436/fCLK 54.5

μ

s

Note 2

27.25

μ

s

Note 2

13.625

μ

s

Note 2

0 1 1 fCLK/6 328/fCLK 41

μ

s

Note 2

20.5

μ

s

Note 2

10.25

μ

s

Note 2

1 0 0 fCLK/5 274/fCLK

Setting

prohibited

34.25

μ

s

Note 2

17.125

μ

s

Note 2

8.5625

μ

s

Note 2

1 0 1 fCLK/4 220/fCLK 55

μ

s

Note 2

27.5

μ

s

Note 2

13.75

μ

s

Note 2

6.875

μ

s

Note 2

1 1 0 fCLK/2

4 f

CLK

112/fCLK

Setting

prohibited

28

μ

s

Note 2

14

μ

s

Note 2

7

μ

s

Note 2

3.5

μ

s

Note 2

1 1 1

0 0 Normal 1

fCLK/1 2 fCLK

54 f

AD

(number

of

sampling

clock:

11 f

AD

)

56/fCLK 56

μ

s

Note 2

14

μ

s

Note 2

7

μ

s

Note 2

3.5

μ

s

Note 2

Setting

prohibited

0 0 0 fCLK/32 2170/fCLK Setting

prohibited

67.8125

μ

s

0 0 1 fCLK/16 1114/fCLK

Setting

prohibited

69.625

μ

s 34.8125

μ

s

0 1 0 fCLK/8 586/fCLK

73.25

μ

s

Note 2

36.625

μ

s 18.3125

μ

s

0 1 1 fCLK/6 454/fCLK

56.75

μ

s

Note 2

28.375

μ

s 14.1875

μ

s

1 0 0 fCLK/5 388/fCLK

Setting

prohibited

48.5

μ

s

Note 2

24.25

μ

s 12.125

μ

s

1 0 1 fCLK/4 322/fCLK 80.5

μ

s

Note 2

40.25

μ

s

Note 2

20.125

μ

s 10.0625

μ

s

1 1 0 fCLK/2

58 f

CLK

190/fCLK

Setting

prohibited

47.5

μ

s

Note 2

23.75

μ

s

Note 2

11.875

μ

s 5.9375

μ

s

1 1 1

0 1 Normal 2

fCLK/1 29 fCLK

66 f

AD

(number

of

sampling

clock:

23 f

AD

)

95/fCLK 95

μ

s

Note 2

23.75

μ

s

Note 2

11.875

μ

s

Note 2

5.9375

μ

s Setting

prohibited

0 0 0 fCLK/32 2447/fCLK Setting

prohibited

76.46875

μ

s

Note 2

0 0 1 fCLK/16 1231/fCLK

Setting

prohibited

76.9375

μ

s

Note 2

38.46875

μ

s

Note 2

0 1 0 fCLK/8 623/fCLK 77.875

μ

s

38.9375

μ

s

Note 2

19.46875

μ

s

Note 2

0 1 1 fCLK/6 471/fCLK 58.875

μ

s

29.4375

μ

s

Note 2

14.71875

μ

s

Note 2

1 0 0 fCLK/5 395/fCLK

Setting

prohibited

49.375

μ

s

24.6875

μ

s

Note 2

12.34375

μ

s

Note 2

1 0 1 fCLK/4 319/fCLK

79.75

μ

s

Note 2

39.875

μ

s

19.9375

μ

s

Note 2

9.96875

μ

s

Note 2

1 1 0 fCLK/2 167/fCLK

Setting

prohibited

41.75

μ

s

Note 2

20.875

μ

s

10.4375

μ

s

Note 2

5.21875

μ

s

Note 2

1 1 1

1 0

Low-

voltage 1

fCLK/1

15 f

CLK

76 f

AD

(number

of

sampling

clock:

33 f

AD

)

91/fCLK 91

μ

s

Note 2

22.75

μ

s

Note 2

11.375

μ

s

5.6875

μ

s

Note

Setting

prohibited

0 0 0 fCLK/32 7368/fCLK Setting

prohibited

230.25

μ

s

Note 2

0 0 1 fCLK/16 3688/fCLK

Setting

prohibited

230.5

μ

s

Note 2

115.25

μ

s

Note 2

0 1 0 fCLK/8 1848/fCLK 231

μ

s

Note 2

115.5

μ

s

Note 2

57.75

μ

s

Note 2

0 1 1 fCLK/6 1388/fCLK

173.5

μ

s

Note 2

86.75

μ

s

Note 2

43.375

μ

s

Note 2

1 0 0 fCLK/5 1158/fCLK

Setting

prohibited

144.75

μ

s

Note 2

72.375

μ

s

Note 2

36.1875

μ

s

Note 2

1 0 1 fCLK/4 928/fCLK 232

μ

s 116

μ

s

Note 2

58

μ

s

Note 2

29

μ

s

Note 2

1 1 0 fCLK/2 468/fCLK

Setting

prohibited

117

μ

s 58.5

μ

s

Note 2

29.25

μ

s

Note 2

14.625

μ

s

Note 2

1 1 1

1 1

Low-

voltage 2

f

CLK/1

8 f

CLK

230 f

AD

(number

of

sampling

clock:

187 f

AD

)

238/fCLK 238

μ

s 59.5

μ

s

29.75

μ

s

Note 2

14.875

μ

s

Note 2

Setting

prohibited

(Notes, Cautions and Remark are listed on the next page.)

<R>