RL78/G1A CHAPTER 15 DMA CONTROLLER

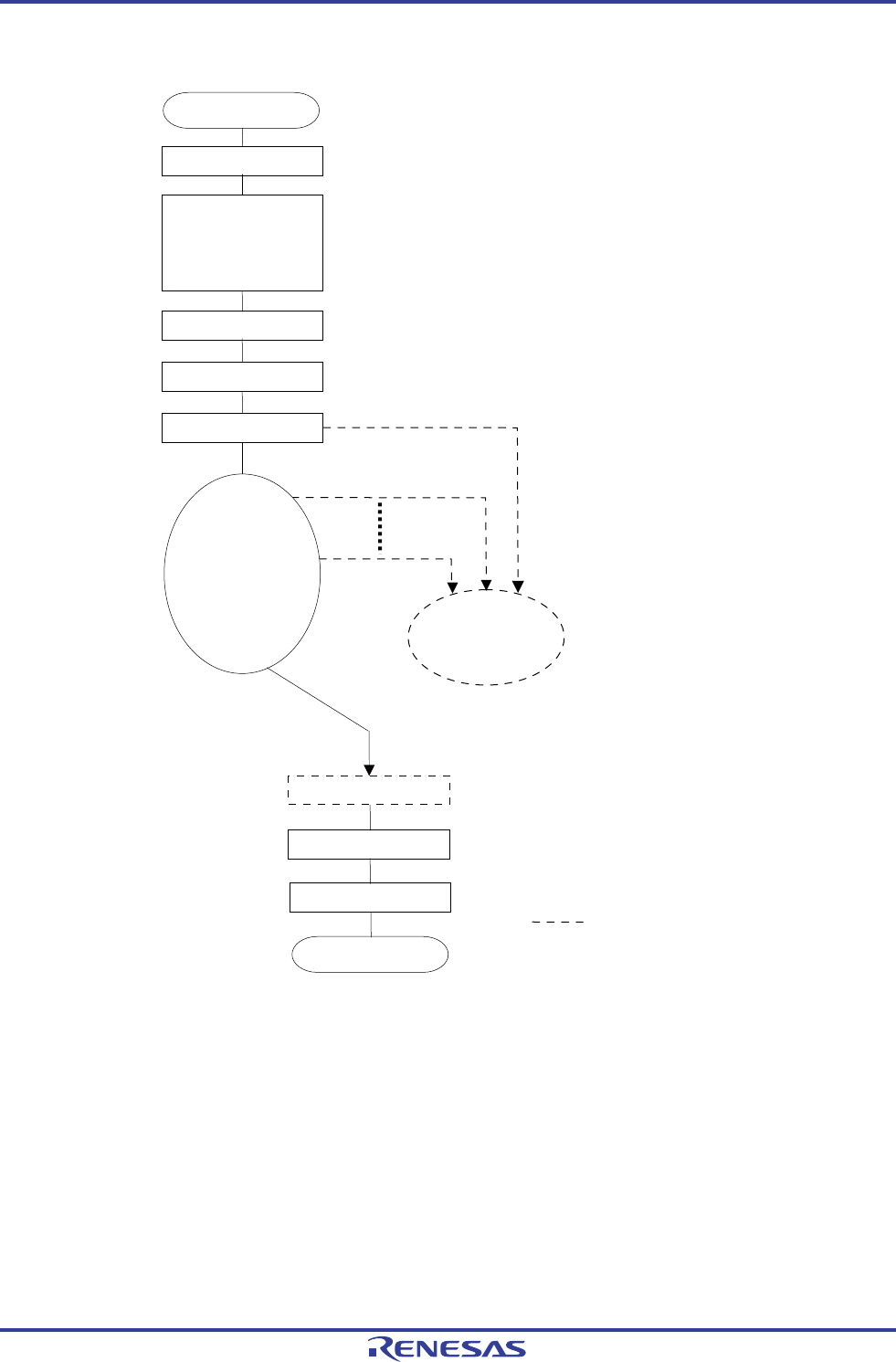

Figure 15-7. Example of Setting for CSI Consecutive Transmission

Setting for CSI transfer

DEN0 = 1

DSA0 = 44H

DRA0 = FB00H

DBC0 = 0100H

DMC0 = 48H

DEN0 = 0

DST0 = 1

STG0 = 1

Start

DMA0 is started.

INTCSI10 occurs.

RETI

End

User program

processing

Occurrence of

INTDMA0

DST0 = 0

Note

DMA0 transfer

CSI

transmission

Hardware operation

Note The DST0 flag is automatically cleared to 0 when a DMA transfer is completed.

Writing the DEN0 flag is enabled only when DST0 = 0. To terminate a DMA transfer without waiting for

occurrence of the interrupt of DMA0 (INTDMA0), set the DST0 bit to 0 and then the DEN0 bit to 0 (for details,

see 15.5.5 Forced termination by software).

The fist trigger for consecutive transmission is not started by the interrupt of CSI. In this example, it start by a software

trigger.

CSI transmission of the second time and onward is automatically executed.

A DMA interrupt (INTDMA0) occurs when the last transmit data has been written to the data register.

R01UH0305EJ0200 Rev.2.00 678

Jul 04, 2013