RL78/G1A CHAPTER 3 CPU ARCHITECTURE

R01UH0305EJ0200 Rev.2.00 95

Jul 04, 2013

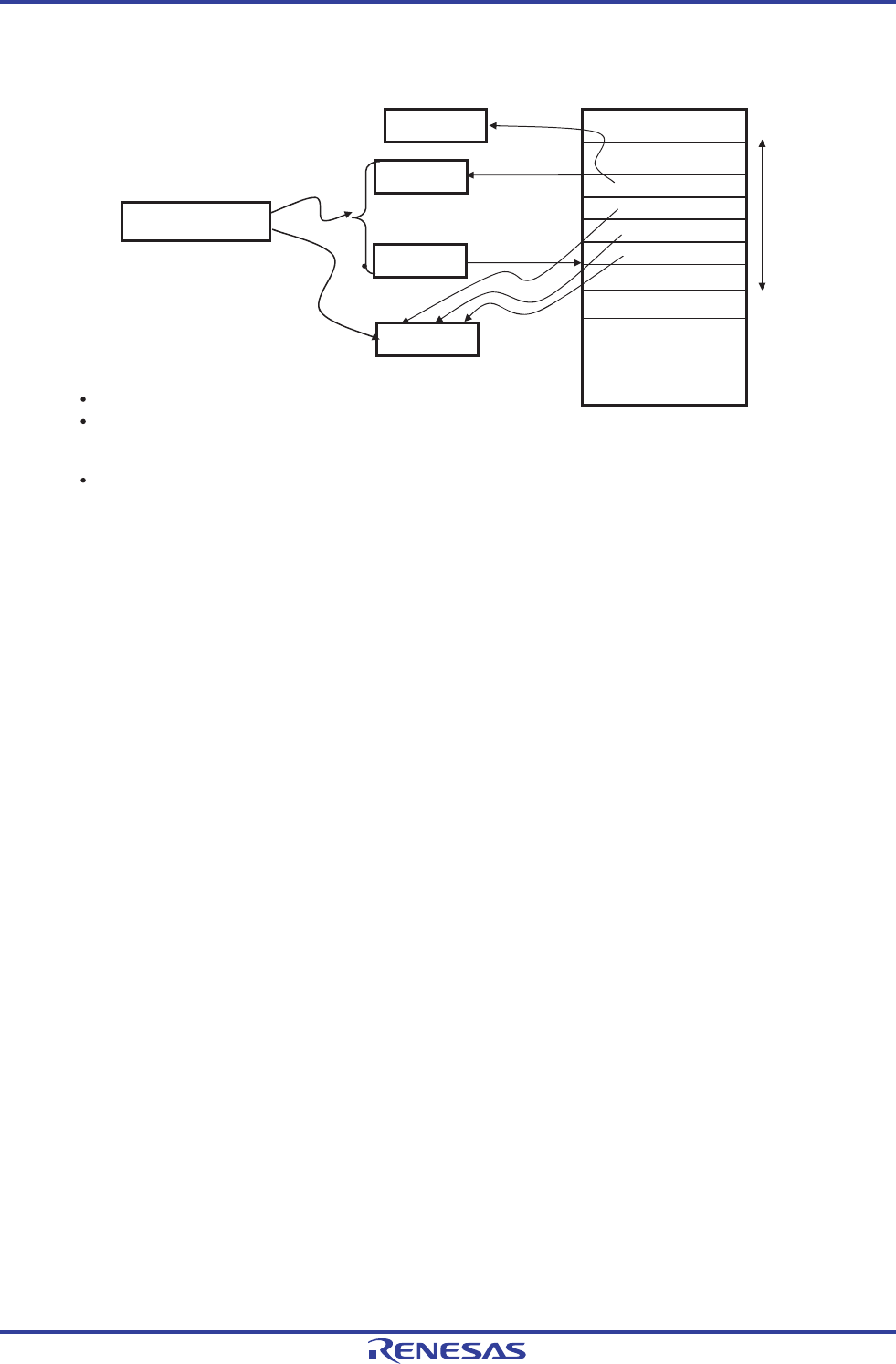

Figure 3-40. Example of RETI, RETB

RETI㧘RETB

SP

F0000H

PC

SP

PSW

Stack

area

Memory

(SP+3)

(SP+2)

SP+3

SP+2

(SP+1)

(SP)

SP+1

SP

SP+4

OP-code

<1>

<1>

Instruction code

<2>

<3>

Stack addressing is specified <1>.

The contents of addresses SP, SP + 1, SP + 2, and SP + 3 are

stored in PC bits 7 to 0, 15 to 8, 19 to 16, and the PSW, respectively

<2>.

The value of SP <3> is increased by four

.