RL78/G1A CHAPTER 1 OUTLINE

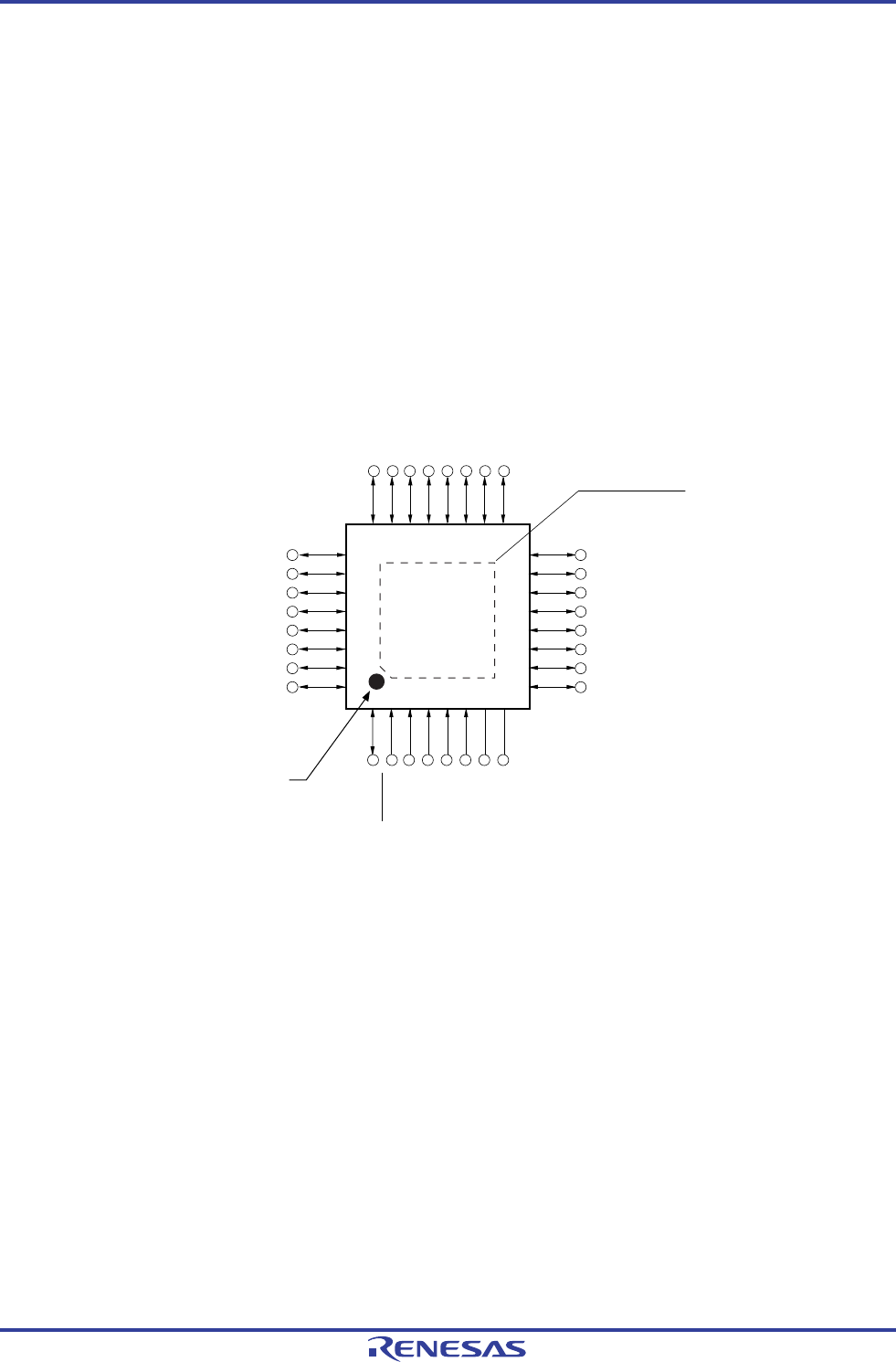

1.3.2 32-pin products

• 32-pin plastic HWQFN (5 × 5 mm, 0.5 mm pitch)

16

15

14

13

12

11

10

9

25

26

27

28

29

30

31

32

24 23 22 21 20 19 18 17

1 2 3 4 5 6 7 8

P24/ANI4/(KR5)

P23/ANI3/(KR4)

P22/ANI2/(KR3)

P21/ANI1/AV

REFM

P20/ANI0/AV

REFP

P03/ANI16/RxD1/TO00/(KR2)

P02/ANI17/TxD1/TI00/(KR1)

P120/ANI19/(KR0)

P51/SO11/INTP2

P50/ANI26/SI11/SDA11/INTP1

P30/ANI27/SCK11/SCL11/INTP3

P70/ANI28/KR0

P31/ANI29/TI03/TO03/PCLBUZ0/INTP4

P62

P61/SDAA0

P60/SCLA0

exposed die pad

AV

SS

AV

DD

P10/ANI18/SCK00/SCL00/(KR0)

P11/ANI20/SI00/SDA00/RxD0/TOOLRxD/(KR1)

P12/ANI21/SO00/TxD0/TOOLTxD/(KR2)

P13/ANI22/SO20/TxD2/(KR3)

P14/ANI23/SI20/SDA20/RxD2/(KR4)

P15/ANI24/SCK20/SCL20/PCLBUZ1/(KR5)

P40/TOOL0

RESET

P137/INTP0

P122/X2/EXCLK

P121/X1

REGC

V

SS

V

DD

INDEX MARK

Caution Connect the REGC pin to Vss via a capacitor (0.47 to 1

μ

F).

Remarks 1. For pin identification, see 1.4 Pin Identification.

2. Functions in parentheses in the above figure can be assigned via settings in the peripheral I/O redirection

register (PIOR). See Figure 4-8 Format of Peripheral I/O Redirection Register (PIOR).

3. It is recommended to connect an exposed die pad to V

ss.

<R>

R01UH0305EJ0200 Rev.2.00 7

Jul 04, 2013