RL78/G1A CHAPTER 6 TIMER ARRAY UNIT

R01UH0305EJ0200 Rev.2.00 255

Jul 04, 2013

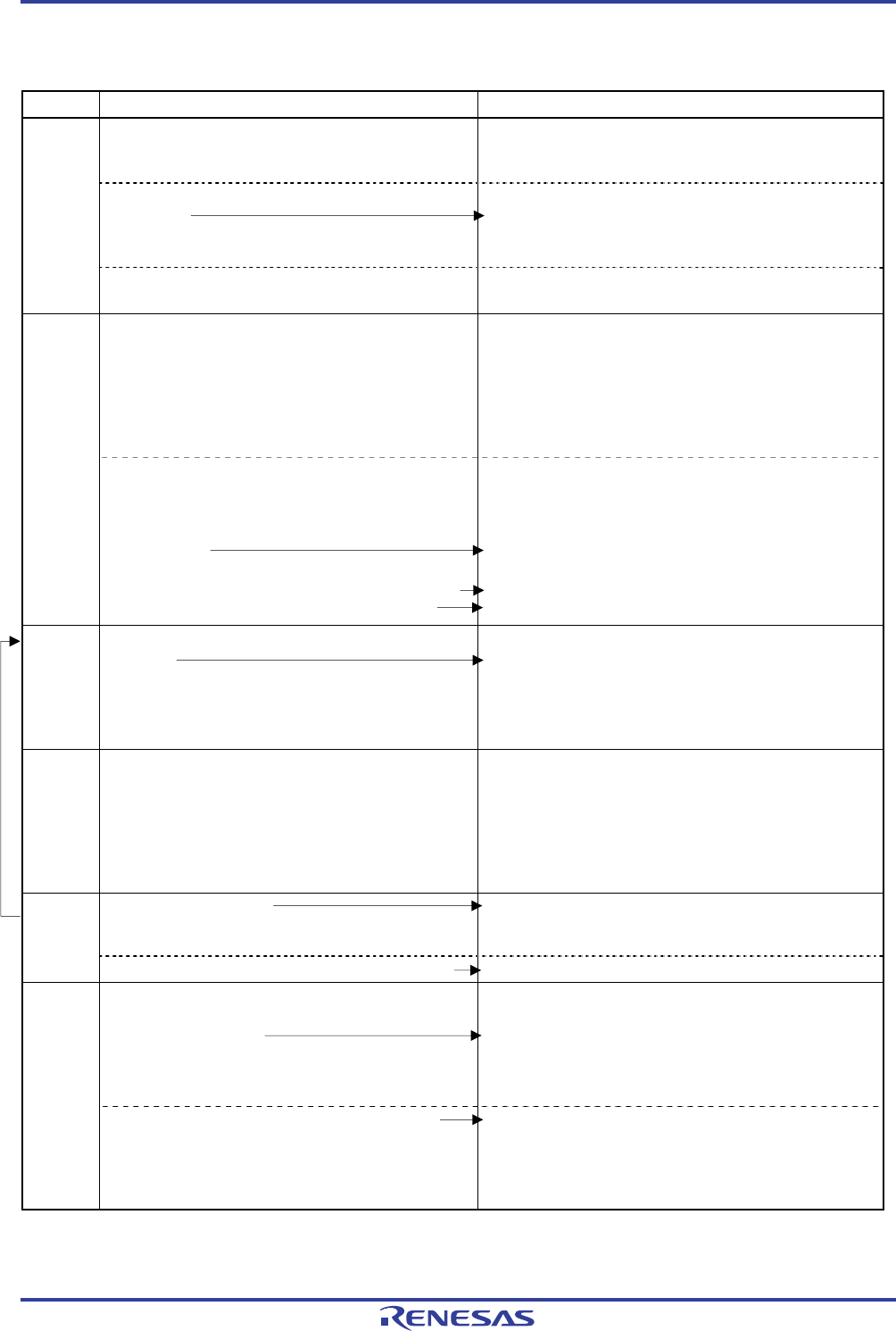

Figure 6-52. Operation Procedure When Frequency Divider Function Is Used

Software Operation Hardware Status

Power-off status

(Clock supply is stopped and writing to each register is

disabled.)

Sets the TAU0EN bit of peripheral enable register 0

(PER0) to 1.

Power-on status. Each channel stops operating.

(Clock supply is started and writing to each register is

enabled.)

TAU

default

setting

Sets timer clock select register 0 (TPS0).

Determines clock frequencies of CK00 to CK03.

Sets corresponding bit of noise filter enable register 1

(NFEN1) to 0 (OFF) or 1 (ON).

Sets timer mode register 0n (TMR0n) (determines

operation mode of channel and selects the detection

edge).

Sets interval (period) value to timer data register 00

(TDR00).

Channel stops operating.

(Clock is supplied and some power is consumed.)

Channel

default

setting

Clears the TOM00 bit of timer output mode register 0

(TOM0) to 0 (master channel output mode).

Clears the TOL00 bit to 0.

Sets the TO00 bit and determines default level of the

TO00 output.

Sets the TOE00 bit to 1 and enables operation of TO00.

Clears the port register and port mode register to 0.

The TO00 pin goes into Hi-Z output state.

The TO00 default setting level is output when the port mode

register is in output mode and the port register is 0.

TO00 does not change because channel stops operating.

The TO00 pin outputs the TO00 set level.

Operation

start

Sets the TOE00 bit to 1 (only when operation is

resumed).

Sets the TS00 bit to 1.

The TS00 bit automatically returns to 0 because it is a

trigger bit.

TE00 = 1, and count operation starts.

Value of the TDR00 register is loaded to timer count

register 00 (TCR00). INTTM00 is generated and TO00

performs toggle operation if the MD000 bit of the TMR00

register is 1.

During

operation

Set value of the TDR00 register can be changed.

The TCR00 register can always be read.

The TSR00 register is not used.

Set values of the TO0 and TOE0 registers can be

changed.

Set values of the TMR00 register, TOM00, and TOL00

bits cannot be changed.

Counter (TCR00) counts down. When count value reaches

0000H, the value of the TDR00 register is loaded to the

TCR00 register again, and the count operation is continued.

By detecting TCR00 = 0000H, INTTM00 is generated and

TO00 performs toggle operation.

After that, the above operation is repeated.

The TT00 bit is set to 1.

The TT00 bit automatically returns to 0 because it is a

trigger bit.

TE00 = 0, and count operation stops.

The TCR00 register holds count value and stops.

The TO00 output is not initialized but holds current status.

Operation

stop

The TOE00 bit is cleared to 0 and value is set to the TO00 bit.

The TO00 pin outputs the TO00 set level.

To hold the TO00 pin output level

Clears the TO00 bit to 0 after the value to be held is

set to the port register.

When holding the TO00 pin output level is not

necessary

Setting not required.

The TO00 pin output level is held by port function.

TAU

stop

The TAU0EN bit of the PER0 register is cleared to 0.

Power-off status

All circuits are initialized and SFR of each channel is also

initialized.

(The TO00 bit is cleared to 0 and the TO00 pin is set to

port mode).

Operation is resumed.

<R>