RL78/G1A CHAPTER 15 DMA CONTROLLER

15.2.3 DMA byte count register n (DBCn)

This is a 10-bit register that is used to set the number of times DMA channel n executes transfer. Be sure to set the

number of times of transfer to this DBCn register before executing DMA transfer (up to 1024 times).

Each time DMA transfer has been executed, this register is automatically decremented. By reading this DBCn register

during DMA transfer, the remaining number of times of transfer can be learned.

The DBCn register can be read or written in 8-bit or 16-bit units. However, it cannot be written during DMA transfer.

Reset signal generation clears this register to 0000H.

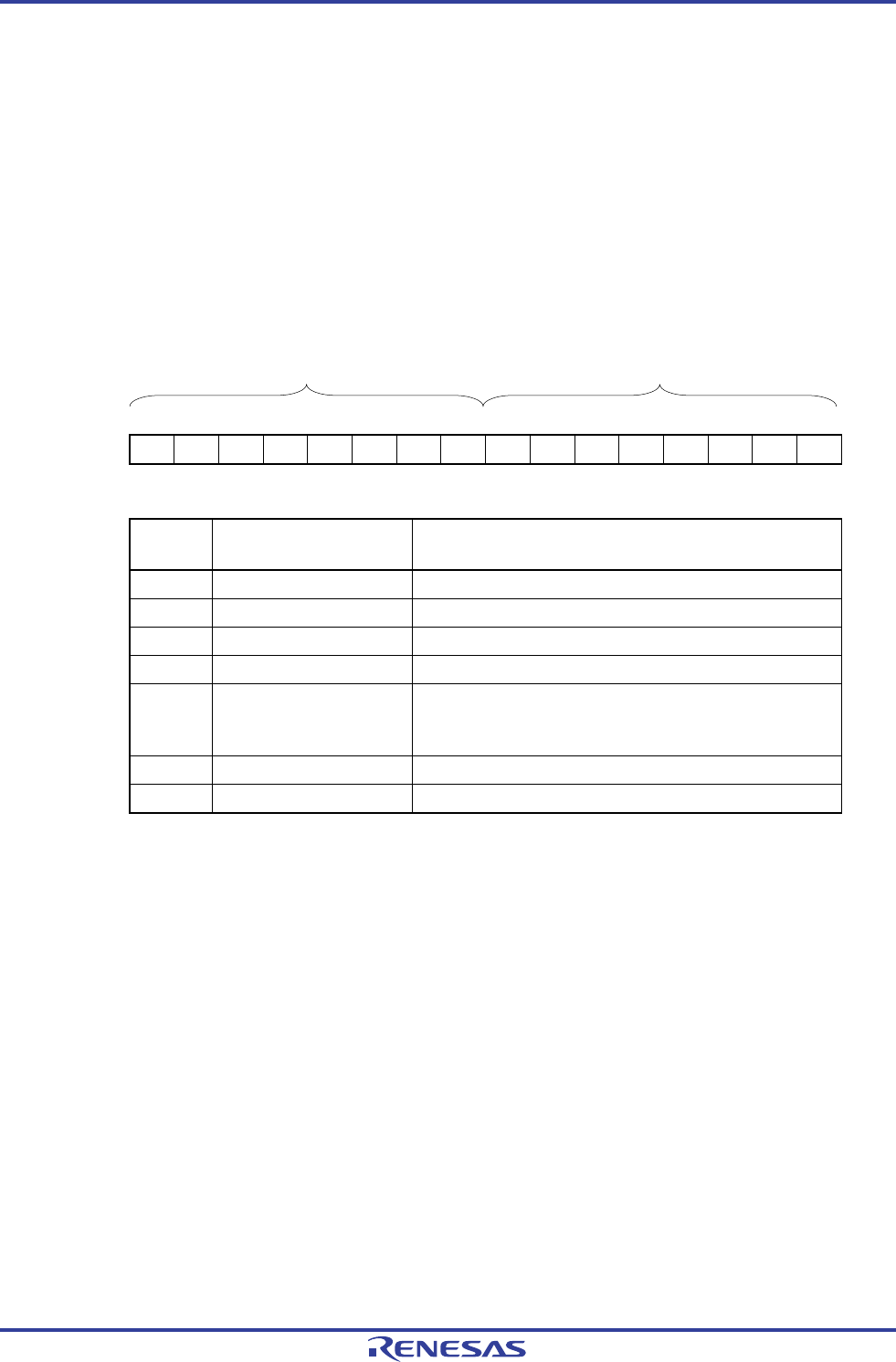

Figure 15-3. Format of DMA Byte Count Register n (DBCn)

Address: FFFB6H, FFFB7H (DBC0), FFFB8H, FFFB9H (DBC1) After reset: 0000H R/W

15 14 13 12 11 10 9 8 7 6 5

DBC0H: FFFB7H

DBC1H: FFFB9H

DBC0L: FFFB6H

DBC1L: FFFB8H

4 3 2 1 0

DBCn 0 0 0 0 0 0

(n = 0, 1)

DBCn[9:0]

Number of Times of Transfer

(When DBCn is Written)

Remaining Number of Times of Transfer

(When DBCn is Read)

000H 1024 Completion of transfer or waiting for 1024 times of DMA transfer

001H 1 Waiting for remaining one time of DMA transfer

002H 2 Waiting for remaining two times of DMA transfer

003H 3 Waiting for remaining three times of DMA transfer

•

•

•

•

•

•

•

•

•

3FEH 1022 Waiting for remaining 1022 times of DMA transfer

Jul 04, 2013

3FFH 1023 Waiting for remaining 1023 times of DMA transfer

Cautions 1. Be sure to clear bits 15 to 10 to “0”.

2. If the general-purpose register is specified or the internal RAM space is exceeded as a

result of continuous transfer, the general-purpose register or SFR space are written or read,

resulting in loss of data in these spaces. Be sure to set the number of times of transfer that

is within the internal RAM space.

Remark n: DMA channel number (n = 0, 1)

R01UH0305EJ0200 Rev.2.00 671