RL78/G1A CHAPTER 29 ELECTRICAL SPECIFICATIONS (T

A = −40 to +85°C)

R01UH0305EJ0200 Rev.2.00 870

Jul 04, 2013

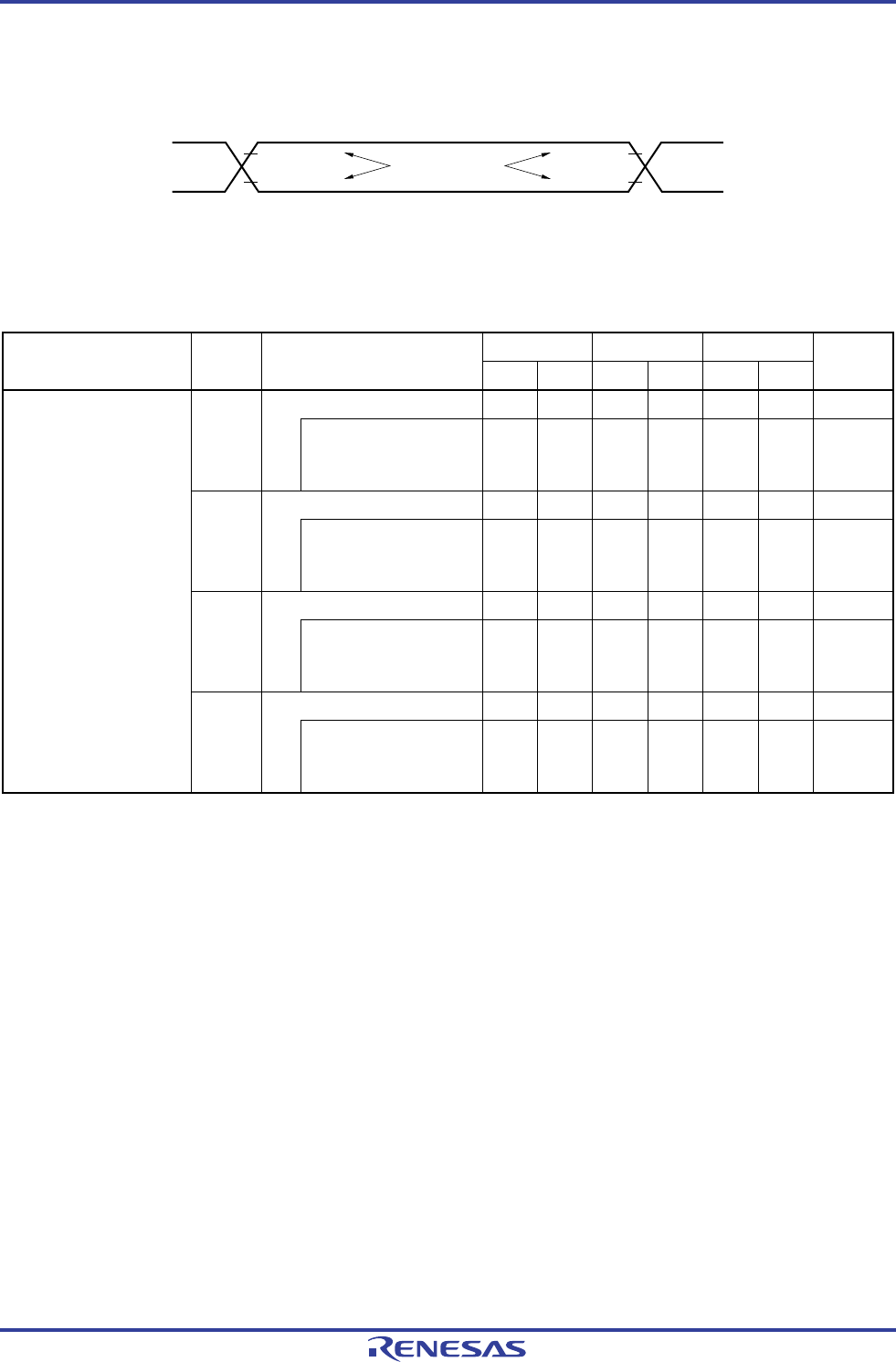

29.5 Peripheral Functions Characteristics

AC Timing Test Points

V

IH

/V

OH

V

IL

/V

OL

Test points

V

IH

/V

OH

V

IL

/V

OL

29.5.1 Serial array unit

(1) During communication at same potential (UART mode)

(T

A = −40 to +85°C, 1.6 V ≤ EVDD0 ≤ VDD ≤ 3.6 V, VSS = EVSS0 = 0 V)

HS

Note 1

LS

Note 2

LV

Note 3

Parameter Symbol Conditions

MIN. MAX. MIN. MAX. MIN. MAX.

Unit

2.4 V ≤ EVDD ≤ 3.6 V fMCK/6 fMCK/6 fMCK/6 bps

Theoretical value of the

maximum transfer rate

f

MCK = fCLK

Note 6

5.3

Note 5

1.3 0.6 Mbps

1.8 V ≤ EVDD ≤ 3.6 V fMCK/6 fMCK/6 fMCK/6 bps

Theoretical value of the

maximum transfer rate

f

MCK = fCLK

Note 6

5.3

Note 5

1.3 0.6 Mbps

1.7 V ≤ EVDD ≤ 3.6 V fMCK/6 fMCK/6 fMCK/6 bps

Theoretical value of the

maximum transfer rate

f

MCK = fCLK

Note 6

5.3

Note 5

1.3

Note 5

0.6 Mbps

1.6 V ≤ EVDD ≤ 3.6 V

−

fMCK/6 fMCK/6

bps

Transfer rate

Note 4

Theoretical value of the

maximum transfer rate

f

MCK = fCLK

Note 6

−

1.3

Note 5

0.6 Mbps

Notes 1. HS is condition of HS (high-speed main) mode.

2. LS is condition of LS (low-speed main) mode.

3. LV is condition of LV (low-voltage main) mode.

4. Transfer rate in the SNOOZE mode is 4800 bps.

5. The following conditions are required for low-voltage interface when EV

DD0 < VDD.

2.4 V ≤ EV

DD0 < 2.7 V : MAX. 2.6 Mbps

1.8 V ≤ EV

DD0 < 2.4 V : MAX. 1.3 Mbps

1.6 V ≤ EV

DD0 < 1.8 V : MAX. 0.6 Mbps

6. f

CLK in each operating mode is as below.

HS (high-speed main) mode: f

CLK = 32 MHz

LS (low-speed main) mode: fCLK = 8 MHz

LV (low-voltage main) mode: f

CLK = 4 MHz

Caution Select the normal input buffer for the RxDq pin and the normal output mode for the TxDq pin by using

port input mode register g (PIMg) and port output mode register g (POMg).

<R>