RL78/G1A CHAPTER 6 TIMER ARRAY UNIT

R01UH0305EJ0200 Rev.2.00 275

Jul 04, 2013

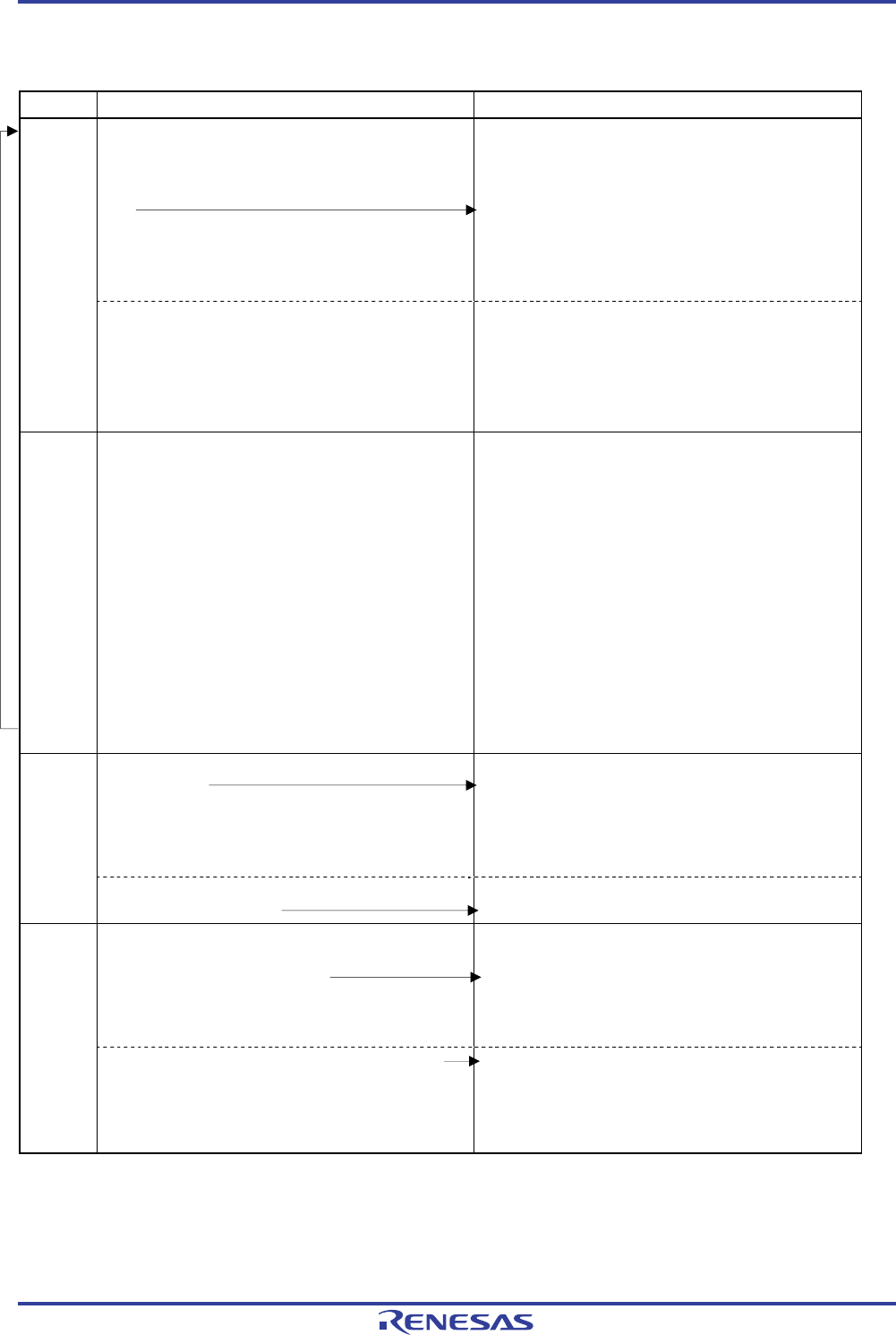

Figure 6-69. Operation Procedure of One-Shot Pulse Output Function (2/2)

Software Operation Hardware Status

Sets the TOEmp bit (slave) to 1 (only when operation is

resumed).

The TSmn (master) and TSmp (slave) bits of timer

channel start register m (TSm) are set to 1 at the same

time.

The TSmn and TSmp bits automatically return to 0

because they are trigger bits.

The TEmn and TEmp bits are set to 1 and the master

channel enters the start trigger detection (the valid edge of

the TImn pin input is detected or the TSmn bit of the

master channel is set to 1) wait status.

Counter stops operating.

Operation

start

Count operation of the master channel is started by start

trigger detection of the master channel.

• Detects the TImn pin input valid edge.

• Sets the TSmn bit of the master channel to 1 by

software

Note

.

Note Do not set the TSmn bit of the slave channel to 1.

Master channel starts counting.

During

operation

Set values of only the CISmn1 and CISmn0 bits of the

TMRmn register can be changed.

Set values of the TMRmp, TDRmn, TDRmp registers,

TOMmn, TOMmp, TOLmn, and TOLmp bits cannot be

changed.

The TCRmn and TCRmp registers can always be read.

The TSRmn and TSRmp registers are not used.

Set values of the TOm and TOEm registers by slave

channel can be changed.

Master channel loads the value of the TDRmn register to

timer count register mn (TCRmn) by the start trigger

detection (the valid edge of the TImn pin input is detected

or the TSmn bit of the master channel is set to 1), and the

counter starts counting down. When the count value

reaches TCRmn = 0000H, the INTTMmn output is

generated, and the counter stops until the next start trigger

detection.

The slave channel, triggered by INTTMmn of the master

channel, loads the value of the TDRmp register to the

TCRmp register, and the counter starts counting down.

The output level of TOmp becomes active one count clock

after generation of INTTMmn from the master channel. It

becomes inactive when TCRmp = 0000H, and the

counting operation is stopped.

After that, the above operation is repeated.

The TTmn (master) and TTmp (slave) bits are set to 1 at

the same time.

The TTmn and TTmp bits automatically return to 0

because they are trigger bits.

TEmn, TEmp = 0, and count operation stops.

The TCRmn and TCRmp registers hold count value and

stop.

The TOmp output is not initialized but holds current

status.

Operation

stop

The TOEmp bit of slave channel is cleared to 0 and

value is set to the TOmp bit.

The TOmp pin outputs the TOmp set level.

To hold the TOmp pin output level

Clears the TOmp bit to 0 after the value to

be held is set to the port register.

When holding the TOmp pin output level is not

necessary

Setting not required.

The TOmp pin output level is held by port function.

TAU

stop

The TAUmEN bit of the PER0 register is cleared to 0.

Power-off status

All circuits are initialized and SFR of each channel is

also initialized.

(The TOmp bit is cleared to 0 and the TOmp pin is set to

port mode.)

Remark m: Unit number (m = 0), n: Channel number (n = 0, 2, 4, 6)

p: Slave channel number (n < p ≤ 7)

However, timer output pin (TOmp) : p = 1, 3 to 7

Operation is resumed.

<R>

<R>