RL78/G1A CHAPTER 19 RESET FUNCTION

19.3 Register for Confirming Reset Source

19.3.1 Reset control flag register (RESF)

Many internal reset generation sources exist in the RL78 microcontroller. The reset control flag register (RESF) is used

to store which source has generated the reset request.

The RESF register can be read by an 8-bit memory manipulation instruction.

RESET input, reset by power-on-reset (POR) circuit, and reading the RESF register clear TRAP, WDTRF, RPERF,

IAWRF, and LVIRF flags.

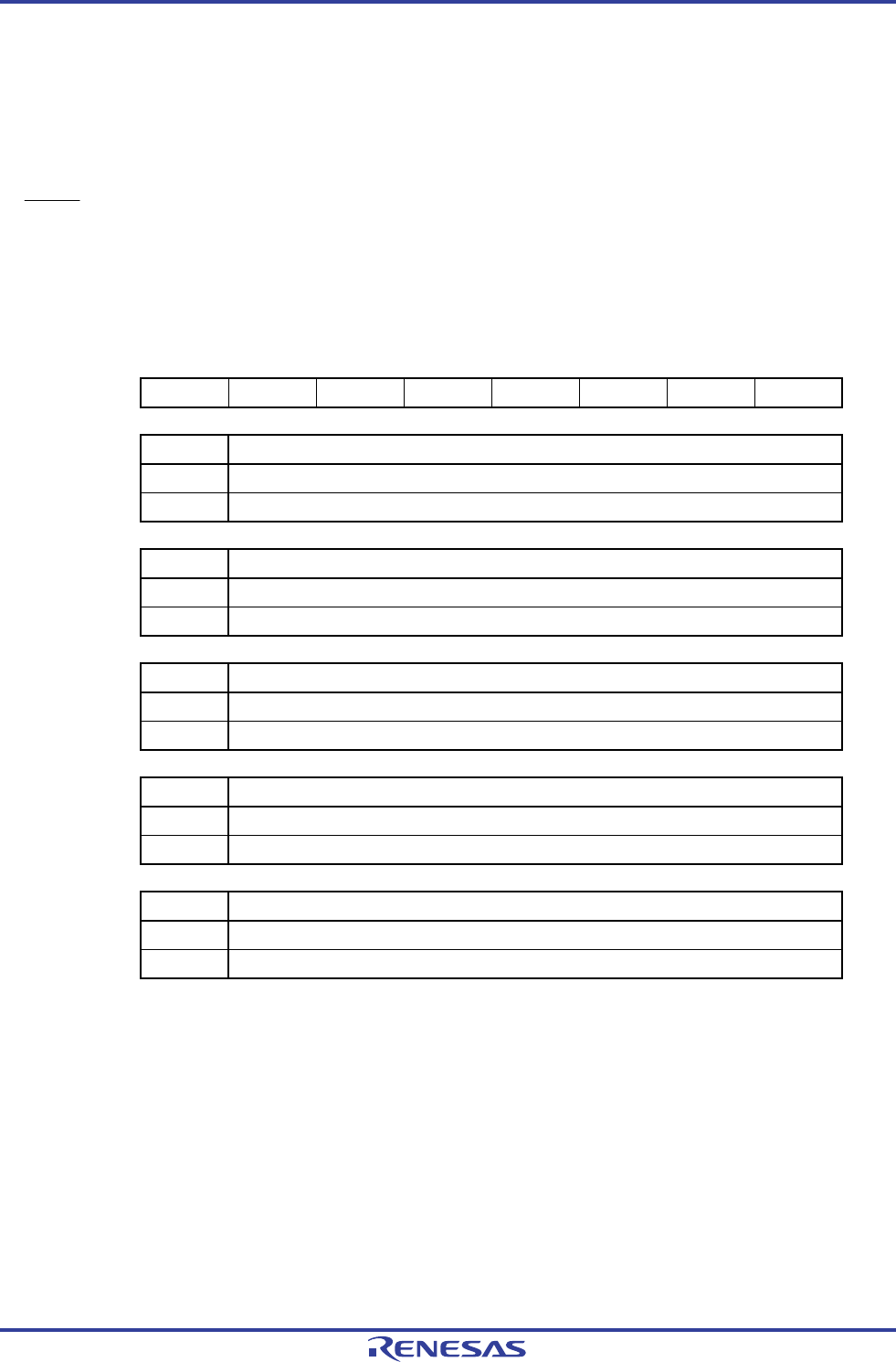

Figure 19-4. Format of Reset Control Flag Register (RESF)

Address: FFFA8H After reset

Note 1

: R

Symbol 7 6 5 4 3 2 1 0

RESF TRAP 0 0 WDTRF 0 RPERF IAWRF LVIRF

<R>

TRAP Internal reset request by execution of illegal instruction

Note 2

0 Internal reset request is not generated, or the RESF register is cleared.

1 Internal reset request is generated.

WDTRF Internal reset request by watchdog timer (WDT)

0 Internal reset request is not generated, or the RESF register is cleared.

1 Internal reset request is generated.

RPERF Internal reset request t by RAM parity

0 Internal reset request is not generated, or the RESF register is cleared.

1 Internal reset request is generated.

IAWRF Internal reset request t by illegal-memory access

0 Internal reset request is not generated, or the RESF register is cleared.

1 Internal reset request is generated.

LVIRF Internal reset request by voltage detector (LVD)

0 Internal reset request is not generated, or the RESF register is cleared.

1 Internal reset request is generated.

Notes 1. The value after reset varies depending on the reset source. See Table 19-3.

2. The illegal instruction is generated when instruction code FFH is executed.

Reset by the illegal instruction execution not issued by emulation with the in-circuit emulator or on-chip

debug emulator.

Cautions 1. Do not read data by a 1-bit memory manipulation instruction.

2. When enabling RAM parity error resets (RPERDIS = 0), be sure to initialize the used RAM area at

data access or the used RAM area + 10 bytes at execution of instruction from the RAM area.

Reset generation enables RAM parity error resets (RPERDIS = 0). For details, see 22.3.3 RAM

parity error detection function.

R01UH0305EJ0200 Rev.2.00 746

Jul 04, 2013