RL78/G1A CHAPTER 22 SAFETY FUNCTIONS

22.2 Registers Used by Safety Functions

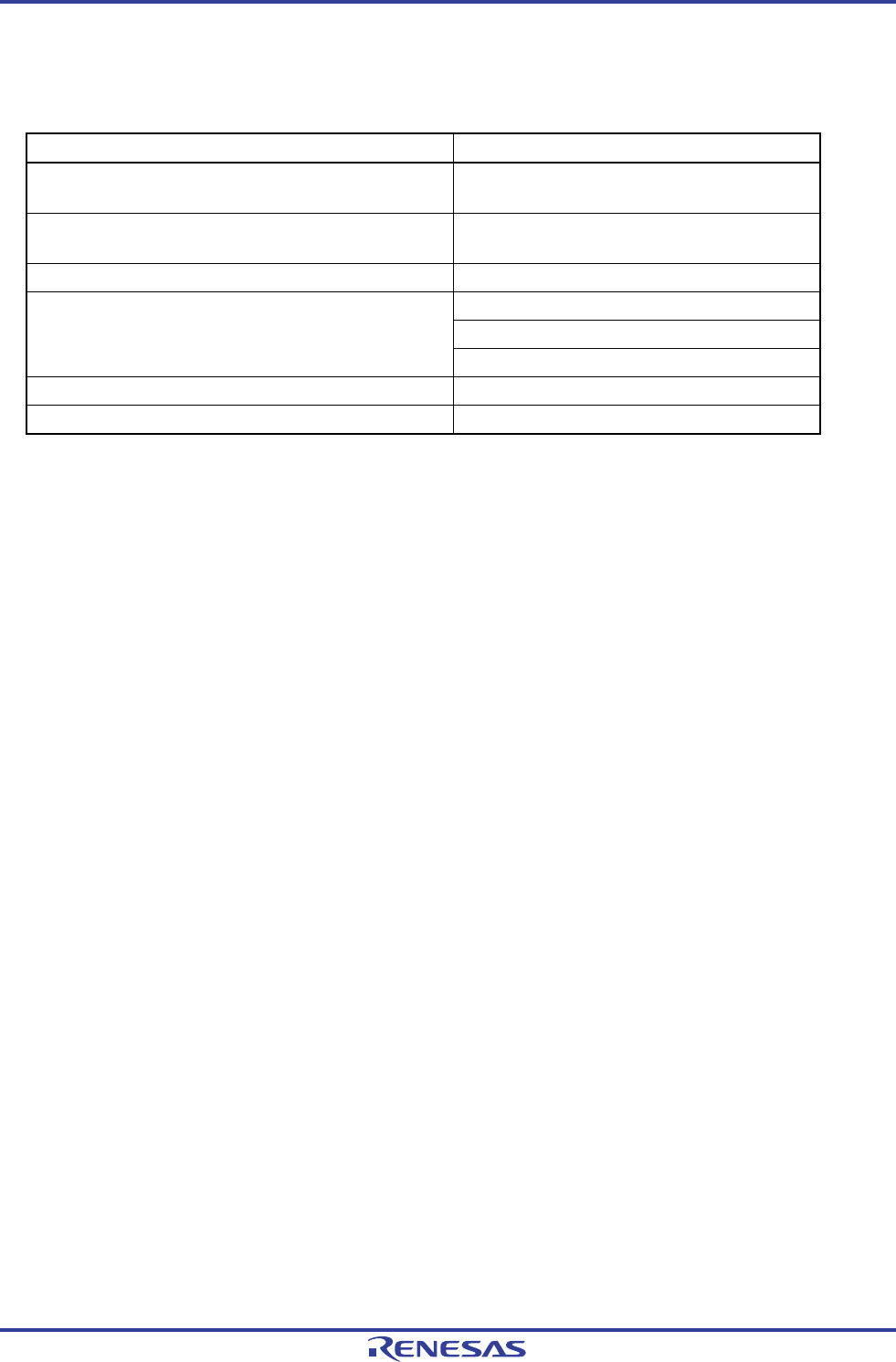

The safety functions use the following registers for each function.

Register Each Function of Safety Function

• Flash memory CRC control register (CRC0CTL)

• Flash memory CRC operation result register (PGCRCL)

Flash memory CRC operation function

(high-speed CRC)

• CRC input register (CRCIN)

• CRC data register (CRCD)

CRC operation function

(general-purpose CRC)

• RAM parity error control register (RPECTL) RAM parity error detection function

RAM guard function

SFR guard function

• Invalid memory access detection control register (IAWCTL)

Invalid memory access detection function

• Timer input select register 0 (TIS0) Frequency detection function

• A/D test register (ADTES) A/D test function

The content of each register is described in 22.3 Operation of Safety Functions.

22.3 Operation of Safety Functions

22.3.1 Flash memory CRC operation function (high-speed CRC)

The IEC60730 standard mandates the checking of data in the flash memory, and recommends using CRC to do it. The

high-speed CRC provided in the RL78/G1A can be used to check the entire code flash memory area during the

initialization routine. The high-speed CRC can be executed only when the program is allocated on the RAM and in the

HALT mode of the main system clock.

The high-speed CRC performs an operation by reading 32-bit data per clock from the flash memory while stopping the

CPU. This function therefore can finish a check in a shorter time (for example, 512

μ

s@32 MHz with 64 KB flash memory).

The CRC generator polynomial used complies with “X

16

+ X

12

+ X

5

+ 1” of CRC-16-CCITT.

The high-speed CRC operates in MSB first order from bit 31 to bit 0.

Caution The CRC operation result might differ during on-chip debugging because the monitor program is

allocated.

Remark The operation result is different between the high-speed CRC and the general CRC, because the general

CRC operates in LSB first order.

22.3.1.1 Flash memory CRC control register (CRC0CTL)

This register is used to control the operation of the high-speed CRC ALU, as well as to specify the operation range.

The CRC0CTL register can be set by a 1-bit or 8-bit memory manipulation instruction.

Reset signal generation clears this register to 00H.

R01UH0305EJ0200 Rev.2.00 773

Jul 04, 2013