RL78/G1A CHAPTER 16 INTERRUPT FUNCTIONS

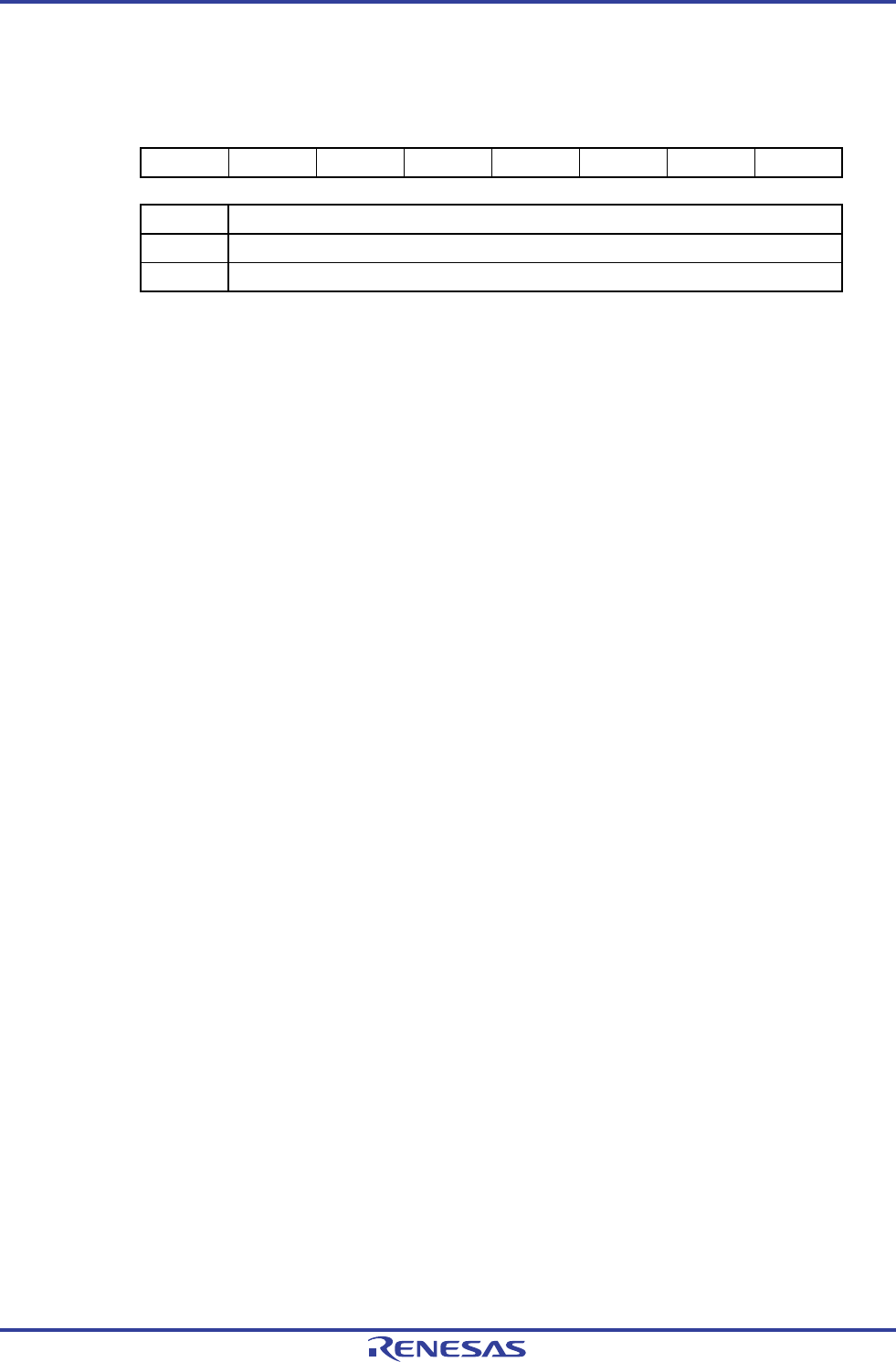

Figure 16-2. Format of Interrupt Request Flag Registers (IF0L, IF0H, IF1L, IF1H, IF2L, IF2H) (2/2)

<R>

Address: FFFD1H After reset: 00H R/W

Symbol <7> 6 <5> 4 3 2 1 <0>

IF2H FLIF 0 MDIF 0 0 0 0 PIF11

XXIFX Interrupt request flag

0 No interrupt request signal is generated

1 Interrupt request is generated, interrupt request status

Cautions 1. The available registers and bits differ depending on the product. For details about the registers

and bits available for each product, see Table 16-2. Be sure to clear bits that are not available to

the initial value.

<R>

2. When manipulating a flag of the interrupt request flag register, use a 1-bit memory manipulation

instruction (CLR1). When describing in C language, use a bit manipulation instruction such as

“IF0L.0 = 0;” or “_asm(“clr1 IF0L, 0”);” because the compiled assembler must be a 1-bit memory

manipulation instruction (CLR1).

If a program is described in C language using an 8-bit memory manipulation instruction such as

“IF0L &= 0xfe;” and compiled, it becomes the assembler of three instructions.

mov a, IF0L

and a, #0FEH

mov IF0L, a

In this case, even if the request flag of the another bit of the same interrupt request flag register

(IF0L) is set to 1 at the timing between “mov a, IF0L” and “mov IF0L, a”, the flag is cleared to 0

at “mov IF0L, a”. Therefore, care must be exercised when using an 8-bit memory manipulation

instruction in C language.

16.3.2 Interrupt mask flag registers (MK0L, MK0H, MK1L, MK1H, MK2L, MK2H)

The interrupt mask flags are used to enable/disable the corresponding maskable interrupt.

<R>

The MK0L, MK0H, MK1L, MK1H, MK2L, and MK2H registers can be set by a 1-bit or 8-bit memory manipulation

instruction. When the MK0L and MK0H registers, the MK1L and MK1H registers, and the MK2L and MK2H registers are

combined to form 16-bit registers MK0, MK1, and MK2, they can be set by a 16-bit memory manipulation instruction.

Reset signal generation sets these registers to FFH.

Remark If an instruction that writes data to this register is executed, the number of instruction execution clocks

increases by 2 clocks.

R01UH0305EJ0200 Rev.2.00 699

Jul 04, 2013